Inhaltsverzeichnis

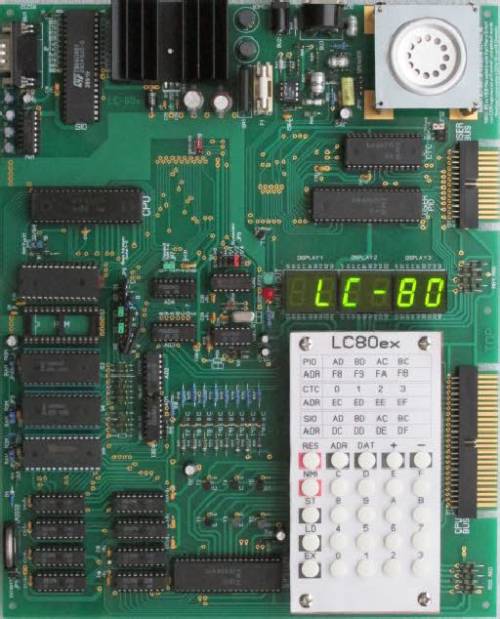

LC80ex

Über den LC-80ex

Der LC-80ex ist eine modifizierte Neuauflage des Lerncomputers LC-80, welcher 1983-85 in der ehemaligen DDR von Ingenieuren des VEB Mikroelektronik Karl Marx Erfurt entwickelt und gebaut wurde. Er basiert auf der für den Export vorgesehenen Version LC-80e, die gegenüber dem ursprünglichen LC-80 einige Verbesserungen aufwies, aber niemals produziert wurde. Es handelt sich hierbei um ein rein privates, nichtkommerzielles Hobbyprojekt. Ausführliche Informationen zum LC-80 und dessen Geschichte hat Volker Pohlers auf seiner Webseite zusammengetragen:

http://hc-ddr.hucki.net/wiki/doku.php/lc80

An dieser Stelle ein großes Dankeschön an Volker für seine umfassende geschichtliche Aufarbeitung der DDR-Rechentechnik, die für dieses Projekt enorm hilfreich war.

Warum eine Neuauflage und wie kam es dazu?

Ende 1985 plante ich den Einstieg in die Computerwelt. Für den zu diesem Zweck angepeilten Z1013 galten jedoch Vorbestellzeiten von einem Jahr und so lange wollte ich nicht warten. Obwohl der alternativ gekaufte LC-80 scheinbar nur die zweite Wahl darstellte, bereute ich dessen Anschaffung nie, denn er verhalf mir trotz (oder gerade wegen) seiner einfachen Bauweise zu tiefgründigem Wissen über die Funktionsweise eines Mikrorechners auf unterster Hardwareebene. Moderne Computer sind weitaus leistungsfähiger und komfortabler, aber aufgrund ihrer Komplexität nicht mehr so leicht zu begreifen. Deswegen gibt es immer noch eine nennenswerte Zahl Interessenten, die sich mit für heutige Verhältnisse primitiv anmutender Retrotechnik befassen und sie verstehen lernen wollen. Z80-basierte Systeme wie der LC-80 sind für diesen Zweck sehr gut geeignet.

Anfang der 90er gelangte ich zufällig an eine unbestückte LC-80 Platine, die jemand achtlos in den Schrott entsorgt hatte. Zwei Jahrzehnte ruhte diese Platine in meinem Bastelfundus, bis sie mir 2014 wieder in die Hände fiel. Eigentlich wollte ich sie nur bestücken, aber dann hielt ich es spontan für eine gute Idee, das Layout für die Nachwelt zu erhalten. Und damit war das Projekt LC-80ex geboren. Nach unzähligen Arbeitsstunden mit Sprintlayout, während derer ich diverse Änderungs- und Verbesserungsvorschläge realisierte, wurde im Dezember 2015 die erste Kleinserie von 20 Platinen in FR4 verewigt und fand innerhalb von zwei Tagen ihre Abnehmer. Wen es interessiert, der kann die ganze Geschichte im Forum auf robotrontechnik.de nachlesen:

http://www.robotrontechnik.de/html/forum/thwb/showtopic.php?threadid=11373

Unterschiede

Unterschiede zwischen LC-80 und LC-80ex

Der LC-80ex basiert auf der nur in wenigen Entwicklungsexemplaren gebauten und nie im Handel erhältlichen Exportversion LC-80e, die bereits folgende Verbesserungen mitbringt:

- erweiterte Adressdecodierung in 4K-Schritten (RAM wird nicht mehr auf andere Bereiche abgebildet)

- höhere Taktfrequenz (1,8 MHz statt 900 KHz)

- Quarzoszillator

- erweiterter Monitor-ROM mit Schachprogramm

Am LC-80ex flossen zusätzliche Modifikationen ein:

- Implementierung einer seriellen Schnittstelle (U856 / Z80-SIO) mit RS232-Pegelwandler

- Taktgenerator mit Frequenzteiler für umschaltbaren Systemtakt (1:1, 1:2, 1:4)

- Anschluß eines externen Taktgenerators (Sandwichplatine) vorbereitet

- Erweiterung der ROM-Steckplätze für 28-polige ICs, z.B. 2764 (24-polige weiterhin unterstützt)

- Steckplätze 3 bis 5 sind alternativ auch mit RAM (6264) bestückbar, dadurch bis zu 28 KByte RAM möglich

- freie Zuweisung der Basisadressen zu den ROM/RAM-Sockeln über Jumperfeld bzw. Stiftleisten

- Batteriebackup für Sockel 5 (bei RAM-Bestückung bleibt dessen Inhalt ohne Stromversorgung erhalten)

- Magnetbandinterface überarbeitet, Bestückung mit aktuellen Dual-OPVs möglich

- Herausführung der Tastatur-Anschlüsse auf Stiftleiste (Tastatur ist abnehmbar)

- diverse Anpassungen (z.B. Rastermaße) zwecks besserer Beschaffbarkeit der Bauteile

Kompatiblität

Der LC-80ex ist weitestgehend kompatibel zum LC-80. Es laufen ohne Anpassung alle für LC-80 und LC-80e geschriebenen Programme, wenn die entsprechenden Monitor-ROMs bestückt und der Systemtakt passend eingestellt werden. Auch der USER-Bus hat exakt die gleiche Anschlußbelegung wie am ursprünglichen LC-80.

Aus layouttechnischen Gründen waren jedoch Änderungen am CPU-Bus und den ROM-Sockeln unvermeidbar. Die Belegung des CPU-Busses weicht zum Teil ab, sodaß für den LC-80 gefertigte Hardwareerweiterungen nicht am CPU-Bus des LC-80ex funktionieren.

Als Kompromiß zugunsten flexiblerer Bestückung der ROM-Sockel ergab sich außerdem die Einschränkung, daß 2Kx8 EPROMs (2716) nur auf dem Sockel Nr.1 verwendbar sind. Dieses „Problem“ ist jedoch leicht zu umgehen, indem die Software einfach in größere EPROMs (2732 oder 2764) umgebrannt wird, die auf allen Sockeln laufen.

Hardwareaufbau

Übersicht

Der Hardwareaufbau des LC-80ex entspricht größtenteils dem des LC-80. Gemäß dem Konzept als Einplatinenrechner sind alle für den Betrieb notwendigen Komponenten direkt auf der Platine bestückt:

Die Kernelemente des Systems bilden der 8-Bit Mikroprozessor Z80 (U880) und dessen Peripheriebausteine Z80- PIO (U855), Z80- CTC (U857) sowie Z80- SIO (U856). Als Anzeige dient ein 7-Segment-LED-Display, für Eingaben ist die Tastatur mit 16 Hexadezimal- und 9 Funktionstasten vorgesehen, der Lautsprecher ermöglicht die Wiedergabe von Tonsignalen. Für die Kommunikation mit der Außenwelt steht eine serielle Schnittstelle zur Verfügung und über das Tape-Interface können Programme auf Magnetband gespeichert oder davon geladen werden. Benutzerspezifische Hardware kann am User-Bus angeschlossen werden und am CPU-Bus sind sämtliche Adress-, Daten- und Steuerleitungen herausgeführt. Fünf 28-polige Sockel dienen der Bestückung mit ROM-Erweiterungen, drei davon können alternativ auch zusätzlichen RAM aufnehmen. Der Systemtakt wird von einem Quarzoszillator mit nachgeschaltetem Frequenzteiler erzeugt.

CPU

Das Herz des LC-80ex ist der Z80-Prozessor im 40-poligen DIP-Gehäuse. Es eignen sich alle kompatiblen Varianten, die mit 5V Betriebsspannung arbeiten. Zu beachten ist, daß die Prozessoren je nach Typ für eine bestimmte maximale Taktfrequenz ausgelegt sind, die für stabilen Betrieb nicht überschritten werden darf. Außerdem müssen die Peripherie-ICs (PIO/SIO/CTC) ebenfalls für die vorgesehene Taktfrequenz spezifiziert sein. Der höchste zulässige Systemtakt richtet sich immer nach der langsamsten Einzelkomponente.

Modernere CMOS- Typen sind wesentlich sparsamer bei der Stromaufnahme (typisch 20 mA), sie brauchen nur einen Bruchteil der Energie ihrer älteren NMOS-Kollegen (typ. 200 mA).

PIO

Der LC-80ex ist mit zwei parallelen Ein-/Ausgabe Bausteinen vom Typ Z80-PIO ausgestattet, die gemäß ihrer vorrangigen Bestimmung als System- bzw. User-PIO bezeichnet werden.

Aufgaben der System- PIO

- Ansteuerung des 7-Segment-Displays (über Treiber-Transistoren)

- Abfrage der Matrixtastatur

- Ausgabe von Tonsignalen zum Lautsprecher und zum Ausgang des Tape-Interface

- Einlesen der Signale vom Eingang des Tape-Interface

Aufgaben der User-PIO

- Port A ist vollständig auf den User-Bus herausgeführt und kann frei verwendet werden

- die Pins 0,1,2 und 3 des Port B liegen mit Einschränkungen ebenfalls am User-Bus an

- Pin 4,5,6 und 7 des Port B werden vom System für die Tastatur-Abfrage verwendet

Während die System-PIO vollständig für interne Prozesse benutzt wird und von außen nicht zugänglich ist, kann über den User-Bus externe Hardware an die User-PIO angebunden werden. Verwendungsmöglichkeiten sind bspw. Steuerungen oder das Einlesen digitaler Signale. Port A steht dem User uneingeschränkt zur Verfügung. Am Port B werden die Pins 4 bis 7 vom System benutzt, dies muß bei der Programmierung beachtet werden. Mehr Details dazu im Abschnitt „User-Bus“. Bezüglich der Typenauswahl und Taktfrequenzen gilt analog das unter „CPU“ gesagte.

CTC

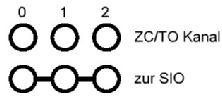

Der Baustein Z80-CTC besitzt vier unabhängige Kanäle, die vom User für Zähler- und Zeitgeberfunktionen programmiert werden können. Die zugehörigen Ein-/Ausgänge sind außerdem auf den User-Bus herausgeführt. Am LC-80ex können die Ausgänge ZC/TO bei Bedarf über einen Jumper die SIO mit dem Baudratentakt versorgen.

Auch für den CTC gelten die unter „CPU“ beschriebenen Bemerkungen zu Taktfrequenz und Typ.

SIO (RS232-Interface)

Als vierte im Bunde der Z80-Familie übernimmt die Z80-SIO die serielle Kommunikation mit der Außenwelt. Diese Komponente wurde beim LC-80ex nachgerüstet, sie existiert nicht in den Urversionen des LC-80. Die SIO hat zwei Kanäle, welche zum komfortablen Datenaustausch mit anderen Geräten nutzbar sind. Praktische Anwendungen sind bspw. das schnelle Laden und Speichern von Programmen am PC oder eine Schnittstelle zu Terminalprogrammen.

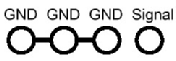

Port B ist zu diesem Zweck bereits über einen MAX232 auf eine Sub-D-Buchse verlegt und kann über Jumper JP12 den Baudratentakt vom CTC beziehen. Zudem sind die Anschlüsse beider Ports auf Stiftleisten herausgeführt, sodaß mit Hilfe von Zusatzhardware auch Port A verfügbar wird.

Achtung!

Aufgrund des verwendeten Pinouts sind für den LC-80ex nur SIO-ICs vom Typ Z80-SIO/0 oder kompatible (z.B. U856) geeignet! Andere Versionen funktionieren wegen abweichender Pinbelegung nicht!

Wie bei CPU, PIO und CTC muß außerdem die für den Typ maximal zulässige Taktfrequenz beachtet werden.

Bestückung

Bitte VOR dem Beginn der Lötarbeiten die nachfolgenden Hinweise und auch die im Abschnitt “Errata” dokumentierten, bekannten Fehler beachten!

IC-Fassungen

Wenn die Bestückung mit metrisch gerasterten Schaltkreisen (DDR-ICs) vorgesehen ist, rate ich von Präzisionsfassungen ab. ICs im 2,5mm Raster passen da nur schlecht rein. Die preiswerten Fassungen mit Doppelfederkontakt eignen sich in diesem Fall wesentlich besser.

Präzisionsfassungen können aber als Sockel für die VQE23 benutzt werden, da diese ausschließlich im 2,54er Raster gebaut wurde. Es empfiehlt sich, die VQE23 während des Verlötens auf die Fassung zu stecken, damit die Ausrichtung exakt stimmt.

Optionale Bestückung

Einige Komponenten müssen für die Grundfunktion des LC-80ex nicht unbedingt bestückt werden. Im Einzelnen sind das:

- die SIO (R2 und C16 entfallen dann auch). Ohne SIO muß der Jumper JP8 gesetzt sein, damit die Interrupt-Kette nicht unterbrochen wird (siehe auch Beschreibung der Jumper).

- der MAX232 (PW1) und die zugehörigen Bauelemente C11 bis C15 sowie BU1 (Sub-D)

- die Bauelemente des Batteriebackups D1, D2, CR2032 und JP1. Bei Nichtbestückung ist anstelle von D2 eine Drahtbrücke einzulöten und der Widerstand R3 kann unten neben R4 plaziert werden

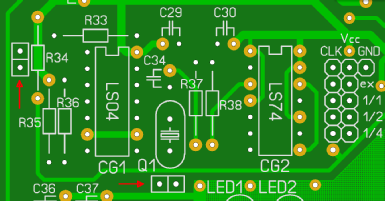

- der Frequenzteiler CG2 (LS74). Wird ein zur Software passender Quarz verwendet und eine Umschaltung des Taktes nicht vorgesehen, kann der Teiler weggelassen werden. Ebenso, wenn die Takterzeugung extern (Sandwichplatine) erfolgt. Der Inverter CG1 (LS04) muß aber in jedem Falle bestückt sein, da er auch die Tasten RES und NMI puffert.

Allgemeines

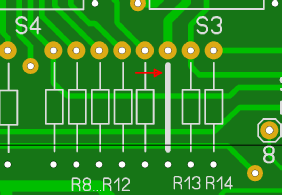

- zwischen R12 und R13 ist eine Drahtbrücke einzulöten:

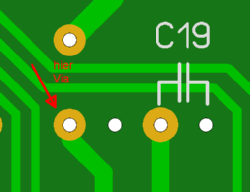

- die Platine hat viele Durchkontaktierungen, die teilweise sehr nahe an Bestückungspunkten liegen, Also genau aufpassen, damit nicht versehentlich ein Bauelement darauf verlötet wird. Kritische Stellen sind z.B. am Abblockkondensator C19, am Widerstand R15 und am Wannenstecker des USER-Bus.

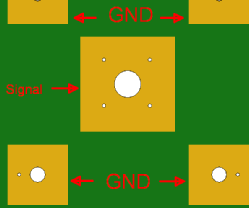

- die Fläche für den Lautsprecher führt auf dem mittleren Pad das Signal und auf den vier äußeren Masse. Wenn keine HS77 verwendet wird, sondern ein über JP11 angeschlossener Kleinlautsprecher, sollte das Zentralpad isoliert werden.

- im Bereich des Taktgenerators befinden sich zwei 2-polige „Jumper“, die nicht verdrahtet sind. Diese sind zusammen mit dem 3-poligen Ende des JP9 als mechanische Stützpunkte für eine separate Taktplatine vorgesehen.

- die Hohlsteckerbuchse sollte mit einem Tropfen Sekundenkleber an der Platine fixiert werden, dies sorgt für besseren mechanischen Halt und entlastet die Lötaugen.

Und nun viel Spaß beim Bestücken!

Errata

Bekannte Fehler

Trotz aller Sorgfalt und x-facher Prüfung haben sich Fehler in das Layout eingeschlichen, die hier dokumentiert sind. Bitte die Version der Platine beachten, da einige Fehler in neueren Auflagen bereits behoben wurden. Bisher nicht entdeckte Bugs bitte an info@lc80ex.de melden.

- Knopfzellenhalter verkehrt herum (Platinenversionen V1 und V2)

Der Knopfzellenhalter für das Batteriebackup ist um 180° verdreht, sodaß die aufgeprägte Polung nicht stimmt. Die Zelle läßt sich trotzdem richtig herum einstecken. Entgegen der Symbole am Halter muß der Pluspol in Richtung Platinenrand zeigen

- C13 im Bestückungsdruck falsch eingezeichnet (nur Platinenversion V1)

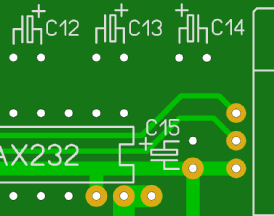

Der Elko C13 (am MAX232) ist falsch herum aufgedruckt. Der Bestückungsplan zeigt die richtige Polung ( + in Richtung Sub-D-Buchse, siehe Bild)

- Bohrungen an Sub-D-Buchse zu klein (nur Platinenversion V1)

An der Sub-D-Buchse sind die Bohrungen der seitlichen Laschen, welche für den mechanischen Halt zuständig sind, zu klein. Diese Laschen sind gabelförmig ausgeführt und das Problem kann durch Wegkneifen der jeweils inneren Hälfte dieser Gabelpins gelöst werden (den abgeknipsten Teil zusätzlich etwas nach oben drücken, damit er nicht auf die Platine stößt).

- Bohrungen an Hohlstecker-Buchse zu klein (nur Platinenversion V1)

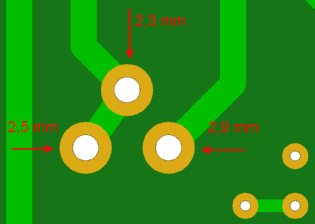

An BU2 (Hohlsteckerbuchse) sind die Bohrungen zu klein. Die seitliche muß auf 2,3mm, die mittlere auf 2,5mm und die hintere (Zentralpin) auf 2,9mm aufgebohrt werden. Vorsichtig von der Leiterseite aus bohren, damit der Restring nicht abgerissen wird. Alternativ die Lötfahnen der Buchse passend machen (vielleicht besser).

Jumper

Beschreibung der Jumper (gültig ab Platinenversion V2)

JP1 - Externe Batterie

Anstelle der CR2032 kann hier eine externe Batterie angeschlossen werden. Die Spannung darf nicht höher sein als die Betriebsspannung des Rechners, also maximal 5V. Die Untergrenze wird durch den auf Sockel Nr.5 gesteckten RAM bestimmt (Spannungsabfall über D1 beachten!). Siehe auch Abschnitt „Batteriebackup“ in der Dokumentation.

JP2/JP3/JP4 - RAM/ROM Select

Ist auf den Typ des im zugehörigen Sockel bestückten Speichers (RAM oder ROM) einzustellen. Fehlstellung führt bei RAM zu Nichtbeschreibbarkeit und kann bei ROM den Verlust oder die Beschädigung des Inhaltes zur Folge haben. Siehe auch Abschnitt „Speicherbestückung“ in der Dokumentation.

JP5 - ROM Typ Sockel 1

Ist abhängig von der Größe des in Sockel 1 bestückten ROMs einzustellen.

- Position „16“ → 2Kx8 (z.B. 2716 / 28C16)

- Position „32/64“ → 4Kx8 (z.B. 2732) oder 8Kx8 (z.B. 2764 / 28C64)

Verbindet Pin 23 des Sockels 1 in Stellung „16“ mit Vcc und in Stellung „32/64“ mit A11. Fehlstellung führt bei 4Kx8 oder 8Kx8 ROMs zu Adressierungsfehlern und kann bei 2Kx8 ROMs den Verlust oder die Beschädigung des Inhaltes zur Folge haben. Siehe auch Abschnitt „Speicherbestückung“ in der Dokumentation.

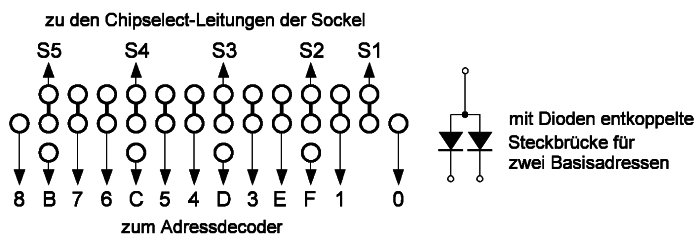

JP6 Basisadressen Sockel 1 bis 5

(Layout gültig ab Platinenversion V2)

Verbindet die Chipselectleitungen der Sockel 1-5 mit den Ausgängen des Adressdecoders.

Hinweis: Die Decoderausgänge „9“ und „A“ sind nicht auf JP6 herausgeführt, können bei Bedarf jedoch direkt am IC AD3 abgegriffen werden (Stiftleiste bestücken).

Die Adressdecodierung des LC-80ex arbeitet in Schritten von 4KB. Um bei 8Kx8 Speichern die volle Größe nutzen zu können, müssen diesen daher zwei Basisadressen zugewiesen werden. Weil die Adressdecoder jedoch keine Opendrain- sondern Pushpull-Ausgänge haben, muß dies mit Hilfe von Entkopplungsdioden erfolgen! Siehe Schema, Kathode zum Adressdecoder, Anode zum Sockel. Keinesfalls dürfen Decoderausgänge mit einfachen Jumperbrücken parallel geschaltet werden, da andernfalls die Decoder- ICs zerstört werden! Die Dioden sollten Schottky-Versionen mit möglichst geringer Flußspannung sein (z.B. BAT86 / BAT48), damit der TTL-Pegel nicht in den verbotenen Bereich geht. 1N4148 sind NICHT geeignet. Unter „Tipps und Tricks“ ist der Bau platzsparender Steckbrücken mit SMD-Dioden beschrieben.

Bei der Zuweisung der Basiadressen zu 8Kx8 Speichern muß eine weitere Besonderheit beachtet werden. Da die Adressleitung A12 bestimmt, ob die oberen oder unteren 4K angesprochen werden, treten zwei Effekte auf. Erstens können nicht zwei gerade oder zwei ungerade Adressen kombiniert werden, sonst wird immer nur eine Hälfte aktiv. Es muß immer eine ungerade mit einer geraden Adresse gepaart werden. Und zweitens muß die Reihenfolge beim Brennen von ROMs beachtet werden. Gerade Basisadressen (z.B. 0000H, 4000H, A000H) sprechen immer die unteren 4K an und ungerade (z.B. 1000H, 5000H, B000H) die oberen 4K.

Beispiel 1:

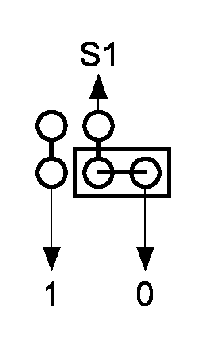

Einem 2716 ROM auf Sockel 1 soll die Basisadresse 0000H zugewiesen werden. Dazu einfache Jumperbrücke zwischen „S1“ und „0“ stecken. (linkes Bild)

Beispiel 2:

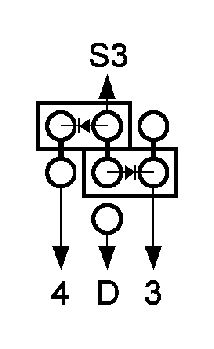

Einem 6264 RAM auf Sockel 3 sollen die Basisadressen 3000H und 4000H zugewiesen werden. Dazu diodenentkoppelte Jumperbrücken mit den Anoden an „S3“ und den Kathoden an „3“ bzw. „4“ setzen. (rechtes Bild)

JP7 - Chipselect RAM 1-4

Mit diesem Jumper kann bestimmt werden, ob die internen RAM-Bänke 1-4 (U214 / 2114) vom Adressdecoder ausgewählt werden oder nicht. Bei gesetzter Jumperbrücke sind die Bänke mit dem Adressdecoder verbunden und werden auf Basisadresse 2000H angesprochen. Bei offenem Jumper sind die Bänke deaktiviert und die Basisadresse 2000H kann anderweitig verwendet werden, um sie bspw. einem auf Sockel 3,4 oder 5 gesteckten 6264 RAM zuzuweisen. Die Bänke 1-4 müssen dann gar nicht bestückt werden.

JP8 - SIO IEI/IEO Bypass

Dieser Jumper muß gesetzt werden, wenn die SIO nicht bestückt ist. Er überbrückt die ansonsten offene Hardware-Interrupt-Kette und schaltet den IEO-Ausgang der USER-PIO direkt an den IEI-Eingang der SYSTEM- PIO.

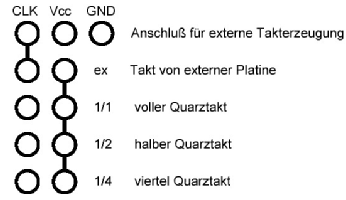

JP9 - Systemtakt

Stellt das Teilerverhältnis zwischen Quarz und Systemclock ein und ist gleichzeitig Connector für die optionale externe Takterzeugung.

Stellt das Teilerverhältnis zwischen Quarz und Systemclock ein und ist gleichzeitig Connector für die optionale externe Takterzeugung.

JP10 - Tastatur

Anschluß für die Tastatur. Die Belegung der Pins wird ausführlich im Abschnitt „Tastatur“ der Dokumentation erklärt.

JP11 - Speaker

JP12 - ZC/TO Kanal SIO Port B

JP13 - TRGx

(ab Platinenversion V2 vorhanden)

Stellt Abgriffe der CTC Ein-/Ausgänge CLK/TRGx zur Verfügung. Unter Verwendung kurzer Jumperkabel zum benachbarten JP12 können damit bspw. die Timerkanäle kaskadiert werden.

Speicherbestückung

Allgemeines

Gegenüber der ersten Version des LC-80 wurde die Adressdecodierung am LC-80e erheblich verbessert und das Manko der Urversion, den RAM auf mehreren Basisadressen anzusprechen, behoben.

Am LC-80ex flossen weitere Verbesserungen ein, die den Speicherausbau noch flexibler gestalten:

- Ausbau der ROM-Steckplätze für 28-polige ICs

- freie Zuordnung der Basisadressen zu den Sockeln mittels Jumperfeld bzw. Steckbrücken

- interner RAM (2114/U214) kann deaktiviert und Bereich 2000-2FFFH anderweitig zugewiesen werden

- die Sockel 3/4/5 können wahlweise mit ROM oder SRAM bestückt werden

Aus layouttechnischen Gründen machte sich ein Kompromiß notwendig, 2Kx8 ROMs (2716) sind ausschließlich auf Sockel 1 lauffähig. Auf den Sockeln 2-5 ist die Adressleitung A11 fest verdrahtet und würde bei 2Kx8 ROM, wo auf diesem Pin Vpp liegt, zu nicht erlaubten Zuständen führen.

Alternativ zu den klassischen UV-EPROMs können auch Flash-ROMs (z.B. 28C16 / 28C64) eingesetzt werden. Dies kommt Usern entgegen, die keine 27xx-kompatiblen Programmer besitzen und verkürzt die Programmierzeit, weil das langwierige UV-Löschen entfällt.

24-polige Speicher-ICs sind rechtsbündig zu bestücken, d.h. Pin 1 des IC auf Pin 3 des Sockels.

Je nach Speichertyp müssen die Jumper JP2, JP3, JP4 und JP5 passend gesetzt werden, da es andernfalls zu Fehlfunktionen oder bei ROM zur Beschädigung des Inhaltes kommen kann.

Die Basisadressen der Sockel S1-S5 sind mittels Jumper (JP6) bzw. Steckbrücken zum Adressdecoder einzustellen. Auch die Zuweisung mehrerer Basisadressen zu einem Sockel mit Hilfe von diodenentkoppelten Steckbrücken ist möglich (notwendig für volle Nutzung von 8Kx8 organisierten Speichern). Dazu unbedingt die Beschreibung im Abschnitt „Jumper“ beachten!

RAM-Bänke 1-4

Wie beim klassischen LC-80 gibt es 4 Speicherbänke für je zwei 1Kx4 SRAM (DIP-18). Damit diese Speicherbänke vom Adressdecoder ausgewählt werden, muß der Jumper JP7 gesetzt sein.

Geeignete Typen: U214, U224, UL224, 2114 oder kompatible

Adressbereiche (JP7 gesetzt):

| Bank 1 | RAM1L/RAM1H | 2000H-23FFH |

| Bank 2 | RAM2L/RAM2H | 2400H-27FFH |

| Bank 3 | RAM3L/RAM3H | 2800H-2BFFH |

| Bank 4 | RAM4L/RAM4H | 2C00H-2FFFH |

Da die 2114 nur 4 Bit breit sind, müssen sie immer paarweise bestückt werden, d.h. jeweils einen auf den L- und den H-Sockel.

ROM Sockel 1 (S1)

- Auf diesem Sockel läuft ausschließlich ROM der Größen 2Kx8, 4Kx8 und 8Kx8.

- Geeignete Typen: 2716, 2732, 2764, 28C16, 28C64 oder kompatible

- Adressbereich: über JP6 bzw. Steckbrücken zum Adressdecoder frei zuweisbar

Der Jumper JP5 muß passend zur Größe gesetzt werden. Für 2Kx8 (2716) auf Position „16“ und für 4Kx8 (2732) bzw. 8Kx8 (2764) auf Position „32/64“. Fehlstellung kann Adressierungsfehler oder Beschädigung des ROM-Inhaltes (insbesondere bei Flashtypen) zur Folge haben.

ROM Sockel 2 (S2)

- Auf diesem Sockel läuft ausschließlich ROM der Größen 4Kx8 und 8Kx8.

- Geeignete Typen: 2732, 2764, 28C64 oder kompatible

- Adressbereich: über JP6 bzw. Steckbrücken zum Adressdecoder frei zuweisbar

Achtung! 2Kx8 organisierte Speicher dürfen hier NICHT bestückt werden!

ROM/RAM Sockel 3 (S3)

- Auf diesem Sockel läuft ROM der Größen 4Kx8 und 8Kx8 sowie RAM der Größe 8Kx8

- Geeignete Typen ROM: 2732, 2764, 28C64 oder kompatible

- Geeignete Typen RAM: 6264 oder kompatible

- Adressbereich: über JP6 bzw. Steckbrücken zum Adressdecoder frei zuweisbar

Die Auswahl des Speichertyps (RAM oder ROM) erfolgt mit dem Jumper JP4. Fehlstellung kann Adressierungsfehler (RAM) oder Beschädigung des Inhaltes (ROM, insbesondere bei Flashtypen) zur Folge haben.

Achtung! 2Kx8 organisierte Speicher dürfen hier NICHT bestückt werden!

ROM/RAM Sockel 4 (S4)

- Wie Sockel 3

- jedoch Auswahl des Speichertyps mit JP3.

ROM/RAM Sockel 5 (S5)

- Wie Sockel 3

- jedoch Auswahl des Speichertyps mit JP2.

- Bei RAM ist zusätzlich batteriegestützte Erhaltung des Inhaltes möglich (siehe Abschnitt Batteriebackup).

Tips und Hinweise

Wie unter „Allgemein“ bereits angesprochen, können auch passende Flashtypen als Alternative zu den UV- EPROMs verwendet werden. Diese müssen aber pinkompatibel und für 5V ausgelegt sein. Im praktischen Test als tauglich haben sich bspw. Atmels 28C16 und 28C64 erwiesen.

Da es möglich ist, jedem Sockel mehr als eine Basisadresse zuzuweisen, können mehrere kleine ROMs in einem größeren zusammengefaßt werden. Zum Beispiel die beiden für 2732 bestimmten 4K-Images des LC- 80e in einem 2764. Dazu „addiert“ man die 4K-Images zu einem 8K-Image und brennt es in den 2764. Das Zusammenfassen geht auf der Kommandozeile ganz einfach mit diesem Befehl:

copy /b 4k-Image1.bin + 4k-Image2.bin 8k-Image.bin

Den Parameter „/b“ nicht vergessen, damit der Binärinhalt unverfälscht kopiert wird. Dem auf diese Art zusammengefassten ROM weist man mittels Diodensteckbrücke die Basisadressen 0 und 1 zu und kann ihn dann so adressieren, als ob es einzelne 4K-ROMs auf verschiedenen Sockeln wären.

Achtung!

Bei der Zuweisung der Basiadressen zu 8Kx8 Speichern muß eine Besonderheit beachtet werden. Da die Adressleitung A12 bestimmt, ob die oberen oder unteren 4K angesprochen werden, treten zwei Effekte auf. Erstens können nicht zwei gerade oder zwei ungerade Adressen kombiniert werden, sonst wird immer nur eine Hälfte aktiv. Es muß immer eine ungerade mit einer geraden Adresse gepaart werden. Und zweitens muß die Reihenfolge beim Brennen von ROMs beachtet werden. Gerade Basisadressen (z.B. 0000H, 4000H, A000H) sprechen immer die unteren 4K an und ungerade (z.B. 1000H, 5000H, B000H) die oberen 4K.

Die Basisadressen „9000H“ und „A000H“ sind nicht auf den Jumper JP6 verdrahtet, sie können bei Bedarf jedoch mit einer Steckbrücke direkt am Adressdecoder abgegriffen werden, wenn dort eine Stiftleiste verlötet wird.

Die Basisadresse „2000H“ ist standardmäßig dem RAM auf den Bänken 1-4 (2114) zugeordnet, wie es der Konfiguration des Ur-LC80 entspricht. Besteht ein Mangel an 2114 Chips oder wird von vornherein mehr als 4K RAM benötigt, kann die Adresse „2000H“ auch einem auf den Sockeln S3, S4 oder S5 bestückten 6264 zugewiesen werden. Der Jumper JP7 bleibt dann offen und der Chipselect des Sockels wird mit Hilfe einer Steckbrücke direkt an die Stiftleiste „2“ des Adressdecoders verkabelt.

Diodenentkoppelte Jumper

Wie im Abschnitt „Jumper“ beschrieben, werden für die Zuweisung mehrerer Basisadressen zu einem RAM/ROM-Sockel diodenentkoppelte Steckbrücken benötigt. Das Layout des JP6 ist so ausgelegt, daß möglichst wenig „Drahtverhau“ entsteht und nebeneinander liegende Bereiche platzsparend mit kleinen, leicht anzufertigenden Steckbrücken zu jumpern sind.

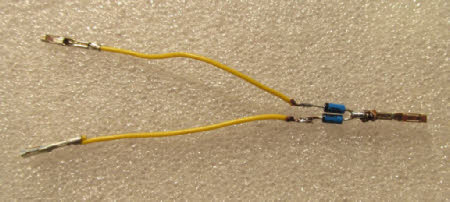

Als Material werden ein Stück Buchsenleiste, SMD-Dioden und Schrumpfschlauch benötigt.

Für die Dioden eignen sich Schottky-Typen mit möglichst geringer Flußspannung im Minimelf- oder SOT23-Gehäuse (z.B. BAT46 / BAT54A). 3-polige mit gemeinsamer ANODE (aufpassen).

Die Herstellung ist denkbar einfach.

2-polige Ausführung

Ein Stück von der Buchsenleiste abschneiden (die gibt es auch zum Abbrechen), Diode zwischen die Pins löten, Schrumpfschlauch drüber und Kathode markieren.

3-polige Ausführung

Analog zur 2-poligen Ausführung, nur mit dreibeiniger SMD-Diode.

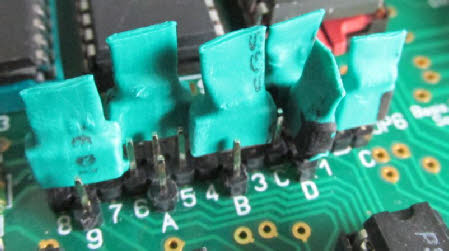

Und so sehen die gesteckten Jumper auf dem Board aus:

Um bei Bedarf räumlich weiter auseinander liegende Bereiche auf den gleichen Sockel zu jumpern, baut man sich Steckbrücken aus normalen Schottky-Dioden (z.B. BAT48 / BAT86) und Kabeln mit Stecker, die sich in dieser Form bspw. aus alten Computern gewinnen lassen oder als sogenannte „Arduino-Steckbrücke female“ gekauft werden können. Nicht im Bild zu sehen, aber auch hier sollte noch Schrumpfschlauch drüber.