# robotron

Speichersteckeinheiten

K 3520; 3521; 3525

K 3820

Betriebsdokumentation

#### Inhaltsverzeichnis

- 1. Anschluß von Speichern

- 1.1. Speicheranschlüsse

- 1.2. Ansteuerbedingungen

- 2. Allgemeine Beschreibung

- 2.1. Technische Daten

- 2.2. Speicherorganisation

- 2.3. Anschlußbedingungen

- 2.4. Bauelementebasis

- 3. Operativspeicher OPS K 3520

- 3.1. Kurzcharakteristik

- 3.2. Technische Daten

- 3.3. Programmierung der STE

- 3.3.1. Programmierfelder der STE

- 3.3:2. AdreBcodierung

- 3.3.3. Auswahl des Speichersperrsignals MEMDI

- 3.3.4. "WAIT"-Bildung

- 3.3.5. Betriebsspannungszuführung 5 PG

- 3.4. Funktionsbeschreibung

- 3.4.1. Verwendungszweck

- 3.4.2. Funktion

- 4. Operativspeicher OPS K 3521

- 4.1. Kurzcharakteristik

- 4.2. Technische Daten

- 4.3. Einsatzbedingungen für den Stütz-Akkumulator

- 4.4. Programmierung der STE

- 4.5. Funktionsbeschreibung

- 4.5.1. Verwendungszweck

- 4.5.2. Funktion

| 5.       | Operativspeicher OPS K 3525                  |

|----------|----------------------------------------------|

| 5.1.     | Kurzcharakteristik                           |

| 5.2.     | Technische Daten                             |

| 5.3.     | Programmierung der STE                       |

| 5.3.1.   | Programmierfelder der STE                    |

| 5.3.2.   | Adressenzuordnung                            |

| 5.3.3.   | Auswahl des Speichersperrsignals MEMDI       |

| 5.3.4.   | "WAIT"→Bildung                               |

| 5.4.     | Funktionsbeschreibung                        |

| 5.4.1.   | Verwendungszweck                             |

| 5.4.2.   | Funktion                                     |

| 6.       | Programmierbarer Festwertspeicher PFS K 3820 |

| 6.1.     | Kurzcharakteristik                           |

| 6.2.     | Technische Daten                             |

| 6.3.     | Programmierung der STE                       |

| 6.3.1.   | Programmierfelder der STE                    |

| 6.3.2.   | Adressenzuordnung                            |

| 6.3.3.   | Belegung der EPROM-Bauelemente auf der STE   |

| 6.3.4.   | Auswahl des Speichersperrsignals MEMDI       |

| 6.3.5.   | "WAIT"-Bildung                               |

| 6.4.     | Funktionsbeschreibung                        |

| 6.4.1.   | Verwendungszweck                             |

| 6.4.2.   | Funktion                                     |

| 6.4.2.1. | Funktionsbeschreibung                        |

| 6.4.2.2. | Adrebdecodierung durch 4 Bit Volladder PS83  |

|          | Serviceschaltnläne                           |

#### 1. Anschluß von Speichern

#### 1.1. Speicheranschlüsse

Der Adreßbus ABO ... AB15 ermöglicht die Adressierung eines 64 K Byte⊷Speichers, dessen Konfiguration nach Belieben zusammengestellt werden kann. Zur Anwendung kommen derzeit folgende Speichersteckeinheiten:

- K 3520 4 K Byte statischer Schreib-Lese-Speicher (s-RAM) n MOS

- K 3525 16 K Byte dynamischer Schreib-Lese-Speicher

- K 3820 16 K Byte programmierbarer Festwertspeicher (EPROM)

- K 3521 4 K Byte Schreib-Lese-Speicher CMOS

Durch die Signale MEMDIT und MEMDI2 des Koppelbusses (siehe Busrichtlinie K 1520) kann die Speicherkapazität von 64 K Byte auf das Doppelte erweitert werden (Codierbrücken K6:2/3 - X7:2/3).

Der gesamte Speicher ist mit dem Systembus über folgende Signale verbunden:

ABO ... AB15 Adresbus DBO ... DB7 Datenbus

MEMRQSpeicheranforderungRDLesesteuersignalWRSchreibsteuersignalMEMDISpeichersperre

RDY Quittungssignal des Speichers

WAIT WAIT-Anforderung an ZRE (Zentrale Recheneinheit)

TAKT Systemtakt

MT Befehlslesezyklus

#### 1.2. Ansteuerbedingungen

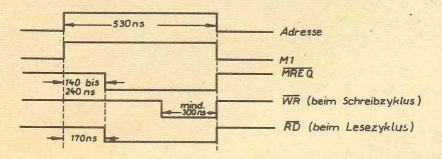

Alle Speichermodule sind durch ihre dynamischen Kennwerte auf das Signalspiel des gemeinsamen Bussystems des K 1520 abgestimmt.

Folgende Bedingungen sind zu beachten:

Die Adresse muß mindestens 530 ns am Bus stabil anliegen. MREQ = low (aktiv) ist 140 ÷ 240 ns nach Anliegen der gültigen Adresse erforderlich. Das Signal bleibt bis zum Adreß-wechsel aktiv. Es muß dabei mindestens 300 ns vor Schreibimpulsende WR = high gültig sein und bis zu dessen Ende anliegen, wenn der Speicher beschrieben wird.

WR = low muß spätestens 300 ns vor dem folgenden Adreßwechsel gewährleistet sein und bis zum Adreßwechsel aktiv bleiben.

Beim Lesen erscheint RD = low (aktiv) spätestens 170 ns nach Adreswechsel und bleibt mindestens bis MREQ nach high aktiv. M1 wird wie die Adresse geschaltet.

Gelesene Daten sind spätestens 450 ns nach Adreswechsel gültig.

#### 2. Allgemeine Beschreibung

#### 2.1. Technische Daten

Steckeinheiten Abmessungen: 215 mm x 170 mm

Steckraster: 20 mm

Steckverbinder: 2 x 58-pol. Betriebsspannung: 5 P  $\triangleq$  + 5 V 5 N  $\triangleq$  - 5 V 5 PG  $\triangleq$  + 5 V

12 P + 12 V

Einsatzklasse: oberhalb 40 °C ist Zwangsbelüftung erforderlich

## 2.2. Speicherorganisation

Die im Punkt 1.1. genannten Speichermodule stehen zur Verfügung, die beliebig und mehr-fach bis zur Kapazitätsgrenze eingesetzt werden können (max. 64 K Byte).

Alle Speichermodule können entsprechend des Speichervolumens über Programmiereinrichtungen auf den Steckeinheiten (Wickelbrücken oder auch Schalter) wahlweise zusammentängenden Adreßbereichen zugeordnet werden, wobei die Speicheranfangsadresse der Steckeinheiten durch 4 K teilbare Werte annehmen.

Dadurch werden geschlossene Speicherbereiche garantiert, die den Erfordernissen der Programmsysteme entsprechen. Adressen dürfen dabei nicht mehrfach belegt werden.

Die Speichersteckeinheiten werden ein- und ausgangsseitig auf den BUS geschaltet. Dadurch ist der Einsatz der Speicher-STE steckplatzunabhängig.

Alle speicherspezifischen Adreß-, Daten- und Steuerleitungen des Busses sind durch Pufferschaltkreise mit Low-Power-Schottky-Eingängen von den Steuer- und Speicherschaltkreisen entkoppelt. Die Pufferschaltkreise der Datenleitungen arbeiten bidirektional und besitzen einen "Tri-state"Zustand. Die erzeugten Steuersignale werden über Open-Kollektor-Baustufen ausgesendet.

Die Geschwindigkeitssynchronisation zwischen ZRE und Speicher erfolgt durch eine "WAIT - Steuerung".

Das auf der entsprechenden STE erzeugte Quittungssignal RDY aktiv low wird gebildet, wenn bei einem gültigen Lese- oder Schreibaufruf die Adresse hardwarenmäßig erkannt wurde.

## 2.3. Anschlußbedingungen

## Signalpegel

low-Potential: Eingänge - 1,0 V ... + 0,85 V Ausgänge 0 V ... + 0,45 V high-Potential: Eingänge + 2,0 V ... + 5,5 V Ausgänge + 2,4 V ... + 5,5 V

#### Signalbelastung

Alle von der Speicher-STE empfangenen Signale (Adreß-und Steuerbits, Dateneingänge) werden mit max. 0,25 mA belastet. Datenausgang ist belastbar mit 15 TTL-LE. Open-Kollektor-Ausgänge der STE treiben max. 10 TTL-LE (16 mA). Diese Ausgänge müssen mindestens einen Lastwiderstand besitzen (auch außerhalb der STE).

## Speicher-STE-spezifische Signale:

Adresse A

ABO ... AB15, 16 Bit

ABO ... AB9 adressieren die Speicherchips (= 1 K Bit), nachfolgende Bits entschlüsseln Adreßgruppen und die höchstwertigen Bits wählen die STE aus.

Daten

DBO ... DB7, 8 Bit

Lesen aus dem Speicher oder Schreiben in den Speicher wird gesteuert durch die Signale RD und WR.

MREQ

Speicheranforderungssignal, es wirkt als Taktsignal für den Speicher (CE Eingänge der Speicherchips).

WR

Befehlssignal "Schreiben in den Speicher"

Es steuert die Funktion "Lesen" oder "Schreiben" der Speicherchips über deren WE-Eingänge.

RD

Befehlssignal "Speicher lesen"

Es bestimmt die Wirkungsrichtung der bidirektionalen Datenpuffer.

MEMDI

Speichersperrsignal

MEMDI1/2

MEMDI wird über den Systembus X1/B09 und die Signale MEMDI1/2 werden über den Koppelbus geführt. Sie sind über Wickelbrücken bzw. Schalter zu programmieren.

- Brücke X6:1 X7:1 geschlossen MEMDI wirksam

- Brücke X6:2 X7:2 geschlossen MEMDIT wirksam

- Brücke X6:3 X7:3 geschlossen MEMDI2 wirksam

Das Sperrsignal schaltet die Datenausgangspuffer in den "Tri-state"-Zustand und sperrt die CE-Eingänge der Speicher. Die Datenausgänge sind hochohmig und können von anderen externen Geräten benutzt werden ohne die entsprechende Speicher-STE zu belasten.

- Normalkonfiguration bei einer maximalen Speicherkapazität von 64 K Byte:

Brücke MEMDI geschlossen

Brücke MEMDI1/2 offen

- AdreBerweiterung über 64 K Byte:

Brücke MEMDI offen

Brücke MEMDII oder MEMDI2 je nach gewünschter Programmierung geschlossen

Beachte: Zusatzverdrahtung auf dem Koppelbus und Zusatzelektronik erforderlich!

RESH

Steuersignal zum Auffrischen dynamischer RAM-Speicher

TAKT, M1

Systemtakt und Kennzeichen "Befehlslesezyklus" - sind Steuersignale zur Bildung des Signals WAIT.

# Signale, die von der Speicher-STE gebildet werden:

Daten

DBO ... DB7, 8 Bit

Die Funktionen "Speicher lesen" oder "Speicher schreiben" werden durch die Steuersignale WR (über WE-Eingänge der Speicherchips) und RD (Eingang DIEN der Datenausgangspuffer ≜ Steuerung der Wirkungsrichtung) gesteuert.

WAIT

Das Signal WAIT aktiv low löst einen "WAIT"-Zyklus im Prozessor aus - während eines Befehlslesezyklus. Dieser Zyklus ist bei einer Speicher-zugriffszeit ≥ 450 ns erforderlich.

RDY

RDY aktiv low, wenn auf der betreffenden STE der adressierte Speicherplatz hardwaremäßig vorhanden ist und zum Datenaustausch zur Verfügung steht.

# 2.4. Bauelementebasis

Zur Anwendung kommen im wesentlichen folgende integrierte Schaltkreise:

|   |       | Realisie      | rung      |         | Allge-<br>mein-<br>typ | Bezeichnung                                    | robo-<br>tron-<br>Nr. | Sachnummer             |

|---|-------|---------------|-----------|---------|------------------------|------------------------------------------------|-----------------------|------------------------|

| D | DR    | RGW           | SU        | NSW     | ESER                   |                                                |                       |                        |

|   |       | MH 3205       |           | 8205    | บ 205                  | schneller 1 aus 8-De-<br>coder                 | SEO5                  | 001 000 000 1 74 00 70 |

|   |       | MH 3212       | K 589/K12 | 8212    | บ 212                  | 8 Bit par. Ein- und<br>Ausgaberegister         | SE12                  | 001-0-174-088          |

|   |       | MH 3216       | K 589/K16 | 8216    | U 216                  | 4 Bit bidirektionaler<br>Bustreiber            | SE16                  | 001-0-174-071          |

|   |       |               |           | SN75361 | W.3.                   | TTL zu MOS Treiber,<br>14-polig                | PZ61                  |                        |

|   |       |               | K 565RU1A | i2107B  | хо7в                   | 4 K dyn. RAM<br>(4096 x 1 Bit)                 | Q 250                 | 001-0-174-075          |

| U | 202 D |               |           | 2102A-4 | X2A4                   | 1 K stat. RAM<br>(1024 x 1 Bit)                | Q 240                 | 001-0-174-048          |

| U | 555   |               |           | 2708    | 4708                   | 1 KByte UV-löschb. PROM                        | Q 260                 | 001-0-507-667          |

|   |       |               |           | s 6508  |                        | 1 K stat. CMOS RAM<br>(1024 x 1 Bit)           | Q 270                 |                        |

| D | 100   | мн 7400       | K 155LA3  | SN7400  | T 100                  | 2-EingNand Gatter,<br>4-fach                   | PS00                  | 001-0-507-701          |

| D | .103  | мн 7403       | _         | SN7403  | Т 103                  | 2-EingNand Gatter,<br>offener Kollektor        | PSO3                  | 001-0-507-702          |

| D | 126   |               |           | TL7426  | т 126                  | 2-EingNand Gatter,<br>4-fach, offener Kollekto | PS26                  | 001-0-507-729          |

| D | 174   | MH '7474      | K 555TM2  | SN7474  | T 174                  | D-FF, 2-fach                                   | PS74                  | 001-0-507-712          |

| D | 183   | ncalw3        | K 155IM3  | SN7483  | т 183                  | 4 Bit Volladder mit<br>Übertrag                | PS83                  | 001-0-174-140          |

| D | 186   |               | K 555LP5  | SN7486  | T 186                  | 2-EingExklusiv-Oder,<br>4-fach                 | PS86                  | 001-0-174-164          |

| D | 200   |               |           | SN74HOO | T 2,00                 | 2-EingNand, 4-fach, schnell                    | PH00                  |                        |

| D | 204   | in the second |           | SN74H04 | Т 204                  | Inverter, 6-fach, schnell                      | PHO4                  | 001-0-507-733          |

| D | 220   |               |           |         | T 220                  | 4-EingNand, 2-fach, schnell                    | PH20                  |                        |

| D | 400   |               | K 158LA3  |         | T 400                  | 2-EingNand, 4-fach,<br>low                     |                       |                        |

Die Wirkungsweise der aufgeführten Bauelemente ist aus der technischen Unterlage "Bauele≕ menteübersicht" zu ersehen.

Die in der Tabelle aufgeführten Äquivalenztypen von Bauelementen verschiedener Hersteller sind die vom Stand April 1980 empfohlenen. Die Angaben sind nicht vollständig.

## 3. Operativspeicher OPS K 3520

## 3.1. Kurzcharakteristik

Der Schreib-Lese-Speicher (Operativspeicher) dient zur Speicherung aller variablen Daten während des Programmablaufs im Mikrorechner K 1520.

Er besteht aus einem 4 K Byte großen statischen nMOS-RAM-Halbleiterspeicher mit den zur Entkopplung, Auswahl und Ansteuerung erforderlichen bipolaren Schaltkreisen.

## 3.2. Technische Daten

Speicherkapazität: Speicherschaltkreistyp:

Zugriffszeit: Betriebsarten:

Datenerhalt:

Stromversorgung:

4 K Byte (Matrix von 4 x 8 Speicherchips) Q 240 (1 K x 1 Bit; nMOS)

≤ 530 ns

"Lesen" oder "Schreiben" als abgeschlossene Zyklen in beliebiger Reihenfolge Gespeicherte Daten gehen bei Abschaltung der Betriebsspannung verloren. Prinzipiell ist ein Datenerhalt möglich, wenn im Ruhezustand des Speichers eine externe Spannung von außen über

Speichers eine externe Spannung von außen über die Klemme 5 PG zugeführt wird. Sie muß > 2 V sein.

5 V ± 5 %, ≤ 0,6 A

für Steuerelektronik und Pufferschaltkreise 5 V  $^+$  5 %,  $\leq$  1,1 A für Speicherschaltkreise

#### 3.3. Programmierung der Steckeinheit

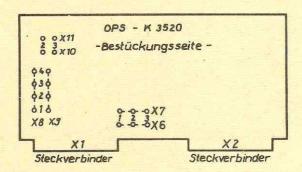

#### 3.3.1. Programmierfelder der Steckeinheit

Die Programmierfelder bestehen aus Wickelstiftpaaren, die wahlweise gebrückt werden können (auch als Schalter ausgeführt).

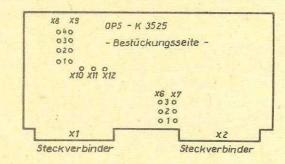

Abb. 1

# 3.3.2. Adrescodierung

Die 16 Adreßleitungen werden auf der Speichersteckeinheit wie folgt verwendet:

ABO ... AB9 - interne Chipadressierung - 1 K Bit

AB10, AB11 - Auswanl einer der 4 1 K-Blöcke auf der STE

AB12 ... AB15 - Auswahl der STE entsprechend der vorgegebenen Adressenzuordnung

#### Programmiervorschrift

Über 4 Codierbrücken X8:1 ... 4, X9:1 ... 4 wird dem Speichermodul ein wählbarer zusammenhängender Adreßbereich von 4 K-Adressen zugeordnet.

Die programmierte Auswahleinrichtung erhält in binärer Verschlüsselung die Anfangsadresse des gewünschten Adresbereiches. Es ergibt sich eine durch 4 K teilhare Adresse.

## Tabelle zur Codierung der Anfangsadresse

|                                                             |               | Codie       | rbrücken     |             |

|-------------------------------------------------------------|---------------|-------------|--------------|-------------|

| Adresbereich                                                | X8:1 - X9:1   | X8:2 - X9:2 | X8:3 - X9:3  | X8:4 - X9:4 |

| 0000 - OFFF                                                 |               | -           | _            | -           |

| 1000 - 1FFF                                                 | -             | _           | -            | Brücke      |

| 2000 - 2FFF                                                 | 2.            |             | Brücke       | =           |

| 3000 - 3FFF                                                 | _,            | _           | Brücke       | Brücke      |

| 4000 - 4FFF                                                 | _             | Brücke      | -            | -           |

| FOOO FFFF                                                   | Brücke        | Brücke      | Brücke       | Brücke      |

| den Brücken<br>sind folgende<br>Wertigkeiten<br>zugeordnet: | <b>≙</b> 32 K | ≙ 16 K      | <b>≜</b> 8 K | ≙ 4 K       |

Beispielsweise entspricht die Codierung aller 4 Brücken einer Speicheranfangsadresse dieser STE von

32 K + 16 K + 8 K + 4 K = 60 K

d. h. die Anfangsadresse dieser STE ist das 60. K = F000H.

# 3.3.3. Auswahl des Speichersperrsignals MEMDI

#### Wickelbrücken

|        | AUDIO    | X6:1 - X7:1 | X6:2 - X7:2 | X6:3 - X7:3 |

|--------|----------|-------------|-------------|-------------|

| MEMDI  | (X1:B09) | Brücke      | - 1         | _           |

| MEMDIT | (X2:A21) |             | Brücke      | -           |

| MEMDI2 | (X2:B21) | _           |             | Brücke      |

Bei Bestückung mit Schaltern entspricht "Brücke" dem geschlossenen Schalter.

# 3.3.4. "WAIT"-Bildung

Von der Zugriffszeit der aufgerufenen Speicherschaltkreise hängt es ab, ob während des Befehlszyklusses im K 2526 eine Zeitverlängerung durch das Steuersignal "WAIT" vorgenommen werden muß.

Für den allgemeinen Anwendungsfall gilt folgende Codierung:

- "WAIT"-Bildung im M1-Zyklus: Brücke X10:3 X11:3 offen

- Unterdrückung der "WAIT"-Bildung: Brücke X10:3 X11:3 geschlossen

## 3.3.5. Betriebsspannungszuführung 5 PG

Im Normalfall werden die RAM-Bausteine über die Betriebsspannung 5 PG versorgt. In Sonderfällen, wo die Anschlüsse 5 PG auf dem Bus nicht belegt sind, kann die Spannung 5 PG steckeinheitenseitig durch Brückung der Wickelstifte X10:2 - X11:2 mit 5 P verbunden werden.

## 3.4. Funktionsbeschreibung

#### 3.4.1. Verwendungszweck

Der OPS K 3520 wird im Erzeugnisprogramm "Dezentrale Datentechnik" als Operativspeicher (statischer Schreib-Lese-Speicher) eingesetzt.

## 3.4.2. Funktion

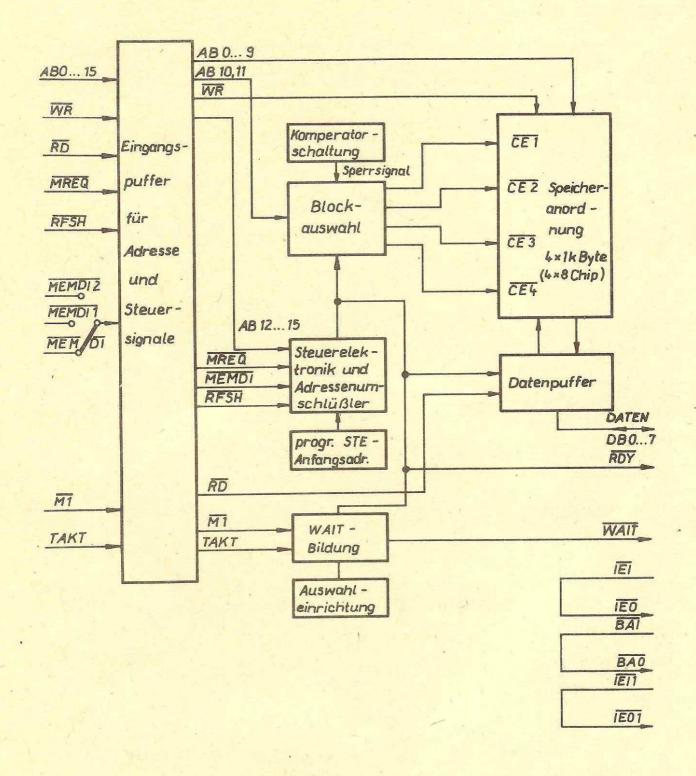

Auf der Steckeinheit befinden sich die Funktionsgruppen:

- Speicher-Matrix

- Ein- und Ausgabepuffer

- Auswahlelektronik

- Steuerelektronik

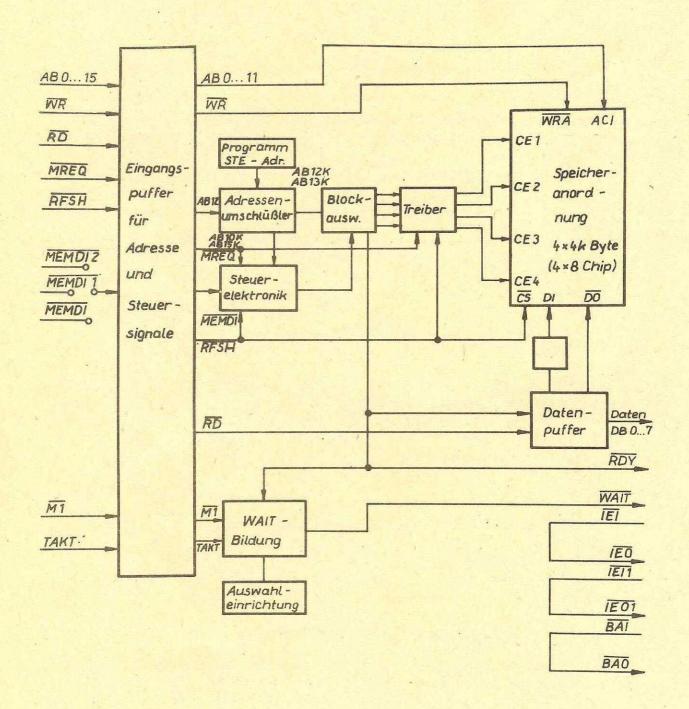

Die Wirkungsweise der Schaltung ist im Blockschaltbild Abb. 2 dargestellt.

Die Speichermatrix besteht aus 4 Gruppen zu je 8 Speicherchips Q 240. Jedes Chip enthält

1 K Bit. Eine Gruppe von 8 Chips bildet einen Speicherbereich von 1 K Byte.

Jede der 4 vorhandenen Blöcke wird durch ein gesondertes CE-Signal aktiviert.

Alle 10 Adreßeingänge der Speicherchips und der Steuereingang WE (Schreib-Lese-Steuerung) sind miteinander verbunden und werden über Schottky-TTL-Pufferschaltkreise SE12 (A2/3/4) gespeist.

Bei den Datenausgangs- und -eingangsleitungen sind jeweils die gleichen Bits der 4 Speicherblöcke parallel geschaltet und mit bidirektional arbeitenden Datenpufferschaltkreisen SE16 (A5/14) verbunden, die die Verbindung mit dem Systembus herstellen. Ist die STE nicht angesteuert, sind die Datenpuffer hochohmig und belasten nicht den Systembus.

Die ebenfalls über SE12 verstärkten Adreßsignale AB10 und AB11 (A3) werden im 1 aus 8-Decoder SE05 (A9) decodiert und bilden eins der 4 Speicheransteuersignale CET ... CE4, wenn gleichzeitig MREQ = low anliegt, MEMDI = high ist und die Adreßsignale AB12 ... AB15 entsprechend der Anfangscodierung der Wickelbrücken ausgewählt wurde. Die Steckeinheit wird angesprochen, wenn alle 4 Eingänge der Auswerteschaltung, die den umgeschlüsselten Adreßbits AB12 ... AB15 entsprechen, den Pegel high besitzen. A7/8 = 0 ist das Freigabesignal für den 1 aus 8-Decoder A9 und gibt das 4er-Nand A7/6 frei, das CS der Ausgabepuffer bildet.

Die Adresdecodierung erfolgt durch den Exklusiv-Oder-Baustein PS86 (A6) in Verbindung mit der programmierten Anfangsadressierung durch das Programmierfeld X8-X9. Ein geschlossener Schalter bzw. eine Brücke schaltet das Potential low auf den Eingang des PS86.

Abb. 2 Blockschaltbild K 3520

Das Freigabesignal, was die Bildung der CET ... CE4-Signale freigibt, aktiviert also gleichzeitig auch die Datenausgangsverstärker zum Datentransfer über den Systembus.

RD steuert dabei die Wirkungsrichtung dieser Puffer. Über A7/6 wird auch das Steuersignal RDY gebildet und die Blockierung der "WAIT"-Bildung-Funktionsgruppe aufgehoben, wenn die Brücke X10:3 - X11:3 nicht gewickelt ist. WAIT wird von einer Schiebekette von 2 D-Flip-Flops durch die Signale MT und TAKT gebildet. WAIT und RDY werden über Open-Kollektor-Baustufen auf den Systembus geführt.

Die Signale zur Durchschaltung der Prioritätenkette für die Interruptbearbeitung und für die Busherrschaft im Systembus IEI, IEO und BAI, BAO sowie IEI1, IEO1 sind auf der Speichersteckeinheit jeweils miteinander gebrückt.

Um bei Netzausfall einen Datenerhalt der Speicherschaltkreise zu ermöglichen (durch eine externe Stützung der Betriebsspannung), ist die Stromversorgung der STE in zwei Kreise aufgeteilt.

Die Speicherchips werden über die Klemmen 5 PG gespeist. Die gespeicherten Informationen bleiben erhalten, wenn im Ruhestand des Speichers die Spannung 5 PG auf eine Schlafspannung von minimal 2 V abgesenkt wird. Die Spannung 5 P für die Puffer-, Auswahl- und Steuerschaltkreise kann dabei abgeschaltet sein.

Damit beim Zu- und Abschaltvorgang der Spannung 5 PG keine undefinierten Ansteuerbedingungen am Speicher wirksam werden können, die zum Datenverlust oder Datenverfälschen

führen, werden die CE-Signale konjunktiv mit einem internen Speichersperrsignal verknüpft. Dieses Sperrsignal, gebildet in der Komperatorschaltung (V5/V11), wird low, sobald die Betriebsspannung 5 P die untere Toleranzgrenze unterschreitet. Damit ist sichergestellt, daß der Treiber PS26 (A11) dann kein aktivierendes Ansteuersignal für die Speicher aussenden kann.

Die Brücke X12-X13 muß geschlossen sein.

Über die mit der Spannung 5 PGI verbundenen Arbeitswiderstände der Open-Kollektor-Treiberbaustufen wird auch im Schlafzustand der erforderliche high-Pegel am CE-Eingang der Speicherchips aufrechterhalten.

Stütz- und Siebkondensatoren in der Leitungsführung der Betriebsspannungen 5 P und 5 PG verhindern kurz- und langfristige Störungen.

## 4. Operativspeicher OPS K 3521

#### 4.1. Kurzcharakteristik

Im Schreib-Lese-Speicher (Operativspeicher) OPS K 3521 werden während des Programmablaufs im Mikrorechner K 1520 variable Daten gespeichert. Im Gegensatz zum OPS K 3520 bleiben die Daten auch nach einer zwischenzeitlichen Programmunterbrechung durch Netzabschaltung am Rechner für eine vorgegebene Haltezeit für die weitere Programmabarbeitung erhalten.

Der OPS K 3521 besteht aus dem STE-Typ 012-7012 mit indirektem Steckverbinder. Er ist ein 4 K Byte statischer Halbleiterspeicher, bestückt mit CMOS-Bausteinen und den zur Entkopplung, Auswahl und Ansteuerung erforderlichen bipolaren Schaltkreisen.

Zusätzlich befindet sich auf der STE die zur Stützung der Speicherbetriebsspannung gehörende Logik einschließlich der Stützspannungsquelle.

## 4.2. Technische Daten

Speicherkapazität: Speicherschaltkreistyp:

Zugriffszeit: Betriebsart:

Datenerhalt:

Stützspannungsquelle:

Stromversorgung:

Stützspannungsüberwachung:

4 K Byte Q 270 bei STE 012-7012 (pinkompatibel) Q 271 bei STE 012-7131 (nicht pinkompatibel) 1 K x 1 Bit; CMOS ≤ 530 ns "Lesen" und "Schreiben" als abgeschlossene Zyklen in beliebiger Reihenfolge. Durch gepufferte NK-Akkumulatoren, die sich auf der STE befinden, wird bei Netzausfall die Betriebsspannung für die Speicherschaltkreise gestützt. Datenhaltezeit ≥ 200 Stunden Reihenschaltung von 3 NK-Knopfzellen mit je 1,2 V und 0,225 mAh Typ KBL 0,225 vom VEB GLZ nach TGL 22807  $5 P = 5 V \pm 5 \%, \le 0,6 A$ für Steuerelektronik und Pufferschaltkreise 5 PG = 5 V ± 5 %, ≤ 40 mA für Speicherschaltkreise und Akkuladestrom

12 NR = 26  $V_{\infty} + \frac{12}{20} \%$ ,  $\leq 10$  mA

Datenerhalt war gesichert.

für die Batteriespannungsüberwachungsschaltung.

Sie muß mind. 200 ms vor dem Zuschalten der

Systemspannungen 5 P und 5 PG anliegen.

Vor dem Zuschalten der Systemspannungen bewertet

eine Kontrollschaltung den Spannungszustand der

Batterie und speichert das Ergebnis ab. Im Betriebszustand kann die Aussage

- Stützspannung war größer

- Stützspannung war gleich

- Stützspannung war kleiner

- Stützspannung war kleiner

- Speicherschaltkreise

angezeigt werden (V9) oder logisch auf den Bus

ausgewertet werden - über das Steuersignal SUE.

LED-Anzeige ein bzw. SUE = low

der Aussage:

Wechselspannung zur Erzeugung der Hilfsspannung

## 4.3. Einsatzbedingungen für den Stütz-Akkumulator

Die NK-Knopfzellen werden in Einzelgehäusen gehaltert, die an der Griffseite der STE angeordnet sind. Das Wechseln der Knopfzellen ist im gestreckten Zustand der STE möglich und kann auch im Betriebszustand des Rechners erfolgen.

Während der Lagerung und des Transportes sind die Knopfzellen auf der STE nicht zu bestücken. Es wird davon ausgegangen, daß bei einer Neubestückung grundsätzlich geladene Zellen zum Einsatz kommen. Im Betriebszustand werden die Zellen mit einem mittleren Ladestrom von 5 mA geladen (ständige Pufferung). Dieser Strom führt auch bei Grenztemperaturen nicht zu Überladungserscheinungen an den Zellen. Der maximal vorkommende Entladestrom bei abgeschaltetem Rechner beträgt 500 µA. Der reale Wert hängt von den konkreten Typen und der Qualität der CMOS-Schaltkreise ab und kann zwischen wenigen µA bis zu 500 µA bei 5 V Betriebsspannung streuen. Aus diesen Vorgaben ergibt sich als Richtwert, daß der Ladezustand der Zellen erhalten wird, wenn die Ladezeit allgemein ein Siebentel der Entladezeit beträgt.

Die Lebensdauer der Akkus wird durch die nutzbare mAh-Kapazität der Zellen bestimmt. Angaben dazu sind in der Einsatzvorschrift des Akkuherstellers und in der TGL 22807 festgelegt. Da die Einsatztemperatur im K 1520 bis zu 60 °C betragen kann, entstehen hohe Belastungen für die NK-Elemente. Temperaturen über 35 °C bewirken zunehmende chemische Umsetzungen der aktiven Masse, die die Kapazität und damit die Lebensdauer erheblich reduzieren. Es gelten daher laut Qualitätsvereinbarung folgende zusätzliche Einsatzbedingungen:

Erfolgt der Betrieb der Zellen im Temperaturbereich bis 40 °C bei zusätzlich insgesamt einer Woche Spitzentemperaturen bis 60 °C, so ergibt sich eine garantierte Lebensdauer der Zellen von einem Jahr, wobei die Lebensdauergrenze bei einer nutzbaren Kapazität von 100 mAh definiert ist. Besteht die Grenztemperatur von 60 °C über einen langen Zeitraum, so verringert sich die definierte Lebensdauer auf 3 Monate.

Aus diesen Garantiewerten ist abzuleiten, daß die Zellen bei Erreichen der angegebenen 100 mAh-Grenze auszuwechseln sind, wenn eine Datenhaltezeit von ≥ 200 Stunden sicher gewährleistet werden muß.

Reduziert man die Anforderungen an die langen Datenhaltezeiten, so lassen sich die Zellen noch nutzen, wenn die Kapazität von 100 mAh unterschritten ist. Die reale thermische Belastung über die Zeit ist aber in der Praxis schwer erfaßbar, so daß der Kapazitätszustand der Zellen nicht exakt vorhersagbar ist. Ein ökonomischer Einsatz der Zellen wird ermöglicht, wenn im Betrieb unter konkreten Einsatzbedingungen im Endprodukt praktische Werte für den Akkutausch abgeleistet werden.

Als Kriterium für die nutzbare Grenzkapazität und den dabei erreichbaren Ladezustand kann die Anzeige der Batteriespannungsüberwachungsschaltung genutzt werden. Wird im Zustand des Datenerhalts die Batteriespannung auf der STE wiederholt gemessen und sinkt bei Ein-haltung normaler Lade- und Entladezyklen unter 3,2 V, dann sind die Zellen auszutauschen.

Neben den zusätzlichen, bereits erwähnten, Qualitätsvereinbarungen bei Temperaturen über 35 °C, gelten die Festlegungen der TGL 22807 und die Behandlungsvorschrift des Akkuherstellers über Lagerung und Einsatz der Zellen.

Ist im Rechner eine Totalentladung von Zellen aufgetreten, sind diese außerhalb des Rechners mittels Ladegerät nach Vorschrift des Herstellers zu laden. Der Ladezustand bei der Lagerung von Zellen ist durch regelmäßige Erhaltungsladungen zu sichern. Eine Ladung von vollständig entladenen Zellen auf der STE mit dem geringen Strom von ca. 5 mA führt nicht zur vollen Ausnutzung der Nennkapazität der Zellen.

Eine Lagerung von entladenen Zellen ist bis zu einer Lagerzeit von einem Jahr ohne Einschränkung der elektrischen Parameter möglich, wenn die Umgebungstemperatur 20  $^{\circ}$ C  $^{\pm}$ 5  $^{\circ}$ C und die relative Luftfeuchte 60 %  $^{\pm}$  15 % eingehalten werden. Danach müssen sie unbedingt mittels Ladegerät 2 bis 3, mal mit Nennströmen geladen und entladen werden, bevor sie im

Rechner eingesetzt werden können.

Knopfzellen anderer Hersteller mit vergleichbaren elektrischen und konstruktiven Daten können eingesetzt werden, wenn die Behandlungsvorschriften dieser Erzeugnisse entsprechende Beachtung finden. Es können sich dabei Einschränkungen in den technischen Daten der Speicher-STE bezüglich Einsatzbedingungen und Datenhaltezeit ergeben.

## 4.4. Programmierung der Steckeinheit

Die Programmierung erfolgt analog der Speichersteckeinheit OPS K 3520 (siehe Punkt 3.3.).

#### 4.5. Funktionsbeschreibung

#### 4.5.1. Verwendung

Der OPS K 3521 wird im Erzeugnisprogramm "Dezentrale Datentechnik" als Operativspeicher (statischer Schreib-Lese-Speicher) eingesetzt, dessen Daten auch bei Systemspannungsabschaltung über eine gewisse Haltezeit gesichert werden.

#### 4.5.2. Funktion

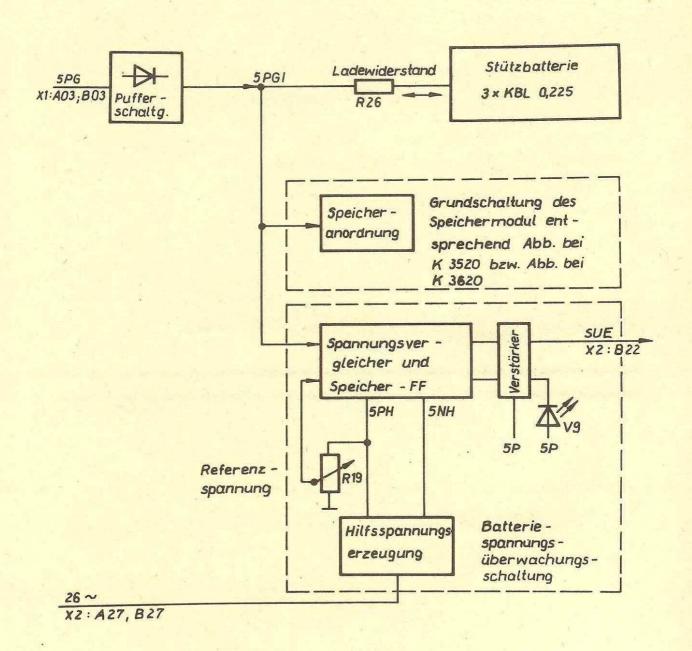

Die Grundschaltung des OPS K 3521 entspricht der des OPS K 3520 (siehe Punkt 3.4.2.). Er ist nur nicht für eine externe Stützung der Betriebsspannung für die Speicherschaltkreise vorgesehen.

Da unterschiedliche CMOS-RAM-Schaltkreise zum Einsatz kommen, gibt es 4 STE-Typen mit gleicher logischer Schaltung:

- STE 012-7012, 012-7017, RAM pinkompatibel zum U 202

- STE 012-7131, 012-7136, RAM nicht pinkompatibel zum U 202

Die STE beinhaltet die Funktionsgruppen:

- Speichermatrix

- Ein- und Ausgabepuffer

- Auswahl- und Steuerelektronik

Sie sind mit denen des OPS K 3520 weitgehend identisch und werden hier nicht beschrieben. Aus dem Blockschaltbild zum OPS K 3521 sind die für den CMOS-Speicher zusätzlichen Schaltteile ersichtlich.

Im Betriebszustand wird die Speichermatrix von 5 PG über Pufferschaltung mit der Betriebsspannung 5 PGI versorgt. Eine Betriebsspannung von 5 PGI ist auch bei den RAM-Bausteinen erforderlich. Diese Spannung bewirkt die Ladung der Stützbatterien G1 ... G3, wobei der Vorwiderstand (R26) den Ladestrom auf ca. 5 mA begrenzt.

Die Pufferschaltung, bestehend aus den Transistorschaltungen V6, V10, blockt bei Ausfall der Systemspannungen (5 P und 5 PG) die Batteriespannung vom Eingang ab, damit keine Ausgleichströme fließen können.

Der Kondensator C4 verhindert beim Zu- und Abschalten der Systemspannungen größere Spannungseinbrüche (dynamischer Stromanstieg über den RAM-Bausteinen beim Zu-und Abschalten). Gleichzeitig werden Prellerscheinungen bei der Kontaktierung der Knopfzellen unterdrückt

Abb. 3 Blockschaltbild K 3521

(C5:1 ... C5:16). Die Spannung der Stützakkus kann im vollgeladenen Zustand ca. 4,1 V betragen. Wird die Spannung < 3 V, liegt der Entladezustand vor. Der Nennwert der Batteriespannung beträgt ca. 3,6 V.

Die um den Spannungsabfall über dem Vorwiderstand R26 verringerte Spannung 5 PGI liegt an den Speicherschaltkreisen an. Es ist die Schlafspannung der CMOS-RAM-Bausteine (bei Q 271 < 2 V). Sie bewirkt, daß Entladeströme von ≤ 500 μA fließen.

Bei kleineren Schlafspannungen als im Datenblatt angegeben, tritt ein Datenverlust im Speicher ein.

Die nachfolgende Batteriespannungsüberwachungsschaltung bewertet den Pegel der Spannung 5 PGI, um den Datenerhalt zu sichern, bevor die eigentlichen Systemspannungen 5 P und 5 PG zugeschaltet werden.

Das Prinzip dieser Schaltung ist aus dem Blockschaltbild ersichtlich.

Am Widerstand R19 wird die erforderliche Referenzspannung eingestellt. Am Eingang 05 des Operationsverstärkers MAA 741 liegt die zu überwachende Batteriespannung des Akkus. Der A16 ist so dimensioniert, daß bei einem Absinken der Batteriespannung unter 2 V die Leuchtdiode V9 verlischt (A16/10 wird low). Gleichzeitig geht das Steuersignal SUE auf low A15/03; A12/11 und ist am Koppelbus X2:B22 auswertbar. Es gilt:

- SUE = high

LED-Anzeige V9 leuchtet: 5 PGI ≥ minimale Schlafspannung

Datenerhalt ist gesichert

$-\overline{SUE} = low$

LED-Anzeige V9 leuchtet nicht: 5 PGI < minimale Schlafspannung bzw. Akkus sind nicht bestückt Datenerhalt ist nicht garantiert

Der FF-Speicherkreis ist so dimensioniert, daß eine Abspeicherung der Vergleicheraussage unmittelbar nach der Einschaltflanke der Hilfsspannung 5 PH erfolgt. Zu diesem Zeitpunkt dürfen die Systemspannungen 5 P und 5 PG nicht anliegen, da sie zu einer Beeinflussung der Stützspannung führen. Ein auftretendes Signal "low" an der Vergleicherbaustufe stellt jederzeit das FF in den Fehlerzustand.

Die für die Funktion dieser Schaltung erforderlichen Hilfsspannungen 5 PH und 5 NH werden durch eine schnelle Gleichrichtung aus einer voreilenden Wechselspannung von 26 V. gewonnen. Für eine sichere Bewertung der Stützspannung muß die Wechselspannung mind. 200 ms vor den Systemspannungen anliegen.

## 5. Operativspeicher OPS K 3525

## 5.1. Kurzcharakteristik

Mit dem Schreib-Lese-Speicher (Operativspeicher) OPS K 3525 werden variable Daten während des Programmablaufs im Mikrorechner K 1520 gespeichert.

Aufgrund des hohen Integrationsgrades der verwendeten Speicherschaltkreise Q 250 können räumlich kleine und billige Speicher aufgebaut werden.

Verwendung findet der Steckeinheitentyp 012-7121 mit indirektem Steckverbinder. Auf der STE befindet sich ein 16 K Byte großer dynamischer Halbleiterspeicher mit 4 K x 1 BitnuMOS-Speicherschaltkreisen.

Außerdem enthält die STE folgende Funktionsgruppen:

- Ein- und Ausgabepuffer

- Auswahlelektronik

- Ansteuerelektronik

## 5.2. Technische Daten

Speicherkapazität:

Speicherschaltkreistyp:

Zugriffszeit: Betriebsarten:

Datenerhalt:

Stromversorgung:

16 K Byte

(Matrix von 4 x 8 Speicherchips vorgesehene Abrüstvarianten: 8 K und 12 K Byte

Q 250

4 K x 1 Bit; nMOS

≤ 350 ns

"Lesen" oder "Schreiben" als abgeschlossene Zyklen in beliebiger Reihenfolge.

Eine statische Ansteuerung des Speichers über einen Zeitraum > 4 µs ist nicht zulässig. Bei Abschaltung der Betriebsspannung geht die Information verloren.

Aller ≤ 2 ms muß durch eine spezielle Refresh-Steuerung die Speicherzelle regeneriert werden. Diese Steuerung übernimmt die ZVE des MR K 2526.

$5 P: + 5 V \pm 5 \%, \le 0,6 A$

12 P: + 12 V ± 5 %, ≤ 0,55 A

5 N: - 5 V ± 5 %, ≤ 50 μA

Der Strombedarf bei 12 P ist sehr stark von der Betriebsart des Speichers abhängig. Der o. g. Wert ergibt sich im Halt-Zustand des MR. Für das Speicherbauelement ist vom Hersteller vorgeschrieben, daß die Spannung an jedem Pin, bezogen auf die Betriebsspannung 5 N, stets positiver als - 0,3 V bleiben muß. Das ist nur gewährleistet, wenn bei Anlegen der Spannungen 12 P und 5 P unbedingt die 5 N am Baustein wirksam ist.

Aufgrund dieser Vorgaben wird für die STE eine Reihenfolge der Spannungszu- und -abschaltung: 5 N - 5 P - 12 P und eine Ausfallüberwachung bei 12 P und 5 P vorgeschrieben.

#### 5.3. Programmierung der Steckeinheit

## 5.3.1. Programmierfelder der STE

Die Programmierfelder können als Wickelstiftpaare oder zum Teil auch als Mikroschalter ausgeführt sein. Entsprechend der Zuordnung der Wickelstiftpaare müssen Brücken gewickelt werden. Die entsprechende Belegung auf der STE ist aus Abb. 4 ersichtlich.

Abb. 4

## 5.3.2. Adressenzuordnung

Die 16 Adressignale werden wie folgt verwendet:

ABO ... AB11 - interne Chipadressierung

AB12, AB13 - Auswahl einer der vier 4 K-Blöcke auf der STE in Abhängigkeit von der Adressenzuordnung der STE

AB14, AB15 - Auswahl der STE in Abhängigkeit der programmierten Adressierung durch X8:3;4 - X9:3;4 (Anfangsadresse des Speicherbereiches der STE)

#### Festlegung der Anfangsadresse der STE:

Über die 4 Wickelbrücken (bzw. Schalter) X8:1 ... X8:4; X9:1 ... X9:4 wird der STE OPS K 3525 ein wählbarer zusammenhängender Adreßbereich von 16 K Byte zugeordnet. Mit dem Programmierfeld kann in binärer Verschlüßselung die Anfangsadresse des gewünschten Adreßbereiches festgelegt werden. Diese Adresse ist ein ganzzahliges Vielfaches von 4 K.

| Adreßbereich                                         |             | Wickelb     | rücken       |             |

|------------------------------------------------------|-------------|-------------|--------------|-------------|

|                                                      | X8:4 - X9:4 | X8:3 - X9:3 | X8:2 - X9:2  | X8:1 - X9:1 |

| 0000 - 3FFF                                          | = =         | -           | 37.          |             |

| 1000 - 4FFF                                          |             | _           |              | Brücke      |

| 2000 - 5FFF                                          |             | Y. C.       | Brücke       | -           |

| 3000 - 6FFF                                          |             |             | Brücke       | Brücke      |

| 4000 - 7FFF                                          | \-          | Brücke      |              | -           |

| BALL STATE                                           |             |             |              |             |

| COOO - FFFF                                          | Brücke      | Brücke      |              | _           |

| Adressenzu-<br>ordnung bei<br>beschalteter<br>Brücke | ≙ 32 K      | ≛ 16 K      | <b>≙</b> 8 K | ≙ 4 K       |

## 5.3.3. Auswahl des Speichersperrsignals MEMDI

|        |                                | 1 W         | ickelbrücken |             |

|--------|--------------------------------|-------------|--------------|-------------|

| Signal | econgressing in Wanter Stayler | X6:1 - X7:1 | X6:2 - X7:2  | X6:3 - X7:3 |

| MEMDI  | (X1:B09)                       | Brücke      | -            | -           |

| MEMDI1 | (X2:A21)                       | -           | Brücke       | 2           |

| MEMDI2 | (X2:B21)                       | -           | -            | Brücke      |

## 5.3.4. Bildung von "WAIT"

Von der Zugriffszeit der aufgerufenen Speicherschaltkreise hängt es ab, ob während des Befehlszyklus im MR K 2526 ein "WAIT"-Zyklus durch das Steuersignal WAIT = O angefordert werden muß.

Für den allgemeinen Anwendungsfall kann die Einstellung wie folgt vorgenommen werden:

- Bildung von "WAIT" im M1-Zyklus: Brücke X10-X11 geschlossen

Brücke X11-X12 offen

- keine "WAIT"-Bildung: Brücke X11-X12 geschlossen

Brücke X10-X11 offen

## 5.4. Funktionsbeschreibung

## 5.4.1. Verwendungszweck

Der OPS K 3525 wird im Erzeugnisprogramm "Dezentrale Datentechnik" als Operativspeicher (dynamischer Schreib-Lese-Speicher) eingesetzt. Mit Hilfe der verwendeten Speicherbausteine sind billigere und kapazitätsmäßig große Operativspeicher im Mikrorechner realisierbar.

#### 5.4.2. Funktion

Auf der Speichersteckeinheit befinden sich folgende Funktionsgruppen:

- Schreib- und Leseansteuerung

- Auswahlelektronik

- Ein- und Ausgabepuffer

Eine eigene Regenerierungsstauerung, die bei Verwendung von dynamischen RAM-Schaltkreisen erforderlich ist, ist auf der Speichersteckeinheit nicht vorhanden.

Das Auffrischen der Speicherinhalte muß durch eine geeignete "Refresh"-Ansteuerung von außen erfolgen; über die Adreßleitungen ABO ... AB6 und das Signal RFSH aktiv low (über den Bus). Die Wirkungsweise der Schaltung geht aus dem Blockschaltbild (Abb. 5) hervor.

Der Speicher besteht aus 4 x 8 Speicherbausteinen Q 250, die eine Kapazität von 4 x 4 K Byte = 16 K Byte ergeben. Die Adreßsignale ABO ... AB11 und das Schreibsteuersignal WR sind durch Schottky-TTL-Pufferschaltkreise SE12 (A3/4/2) vom Bus entkoppelt. Die Signale liegen parallel an allen Speicherbausteinen.

Die Adreßleitungen wählen beim Aufruf Speicherzugriff die entsprechend adressierte Speicherzelle (8 Bit Aufrufbreite) zum Beschreiben oder Lesen aus oder sie adressieren beim Auffrischaufruf eine Zeile von 64 Speicherzellen in jedem Baustein. Bei diesem "RFSH"-

Abb. 5 Blockschaltbild K 3525

Aufruf werden alle 4 Blöcke (4 x 4 K Byte) über den CE-Treiber A5/6 (2-fach TTL-MOS-Treiber) gleichzeitig angesteuert.

Die Auswahl der 4 Speicherblöcke beim Schreib-/Leseaufruf erfolgt über einen 1 aus 8Decoder SE05 (A10) durch Bildung CE1 ... CE4-Signals in Abhängigkeit von den umgeschlüsselten Adreßbits AB12K und AB13K.

Die Ansteuerbedingungen sind:

- Schreib-/Leseaufruf: MREQ . MEMDI . RFSH

- Auffrischaufruf: RFSH . MREQ

Während des Auffrischzyklus werden über A8/12 durch das Signal RFSH = low die CE-Eingänge der Speicherbausteine auf "high" geschaltet. Damit bleiben die Datenausgänge hochohmig und es tritt ausgangsseitig keine Beeinflussung durch die ausgewählte STE auf.

Über den 1 aus 8-Decoder A10 und dem speziellen CE-Treiber P361 A5/6 werden die entsprechenden Blöcke auf der Speichermatrix angewählt. Sobald ein CE-Signal im Schreib- bzw.

Leseaufruf gebildet wird, werden auch die bidirektional arbeitenden Datentreiber SE16

A7 und A11 aktiviert (CS A7/A11 über A9-A8/02).

Das Steuersignal  $\overline{RD}$  steuert dabei die Datenflußrichtung dieser Datentreiber. Beim Lesen ist  $\overline{RD}$  = low und die Daten sind vom Speicher auf den Bus geschaltet.

Da zwischen Datenein- und Datenausgang der Speicherelemente ein Polaritätswechsel vorliegt, müssen die Daten vor dem Einschreiben negiert werden (A8, A12).

Gleichzeitig mit der Bildung des Signals CS für die Datentreiber wird über die Open-Kollektor-Baustufe A15 das Signal RDY = low gebildet und die "WAIT"-Bildung am Eingang R des FF A14 freigegeben, sofern die Brücke X11-X12 nicht geschlossen ist (vergleiche Punkt 2.3.4.).

Bei Speicherelementen mit hoher Zugriffszeit kann beim Befehlslesen somit eine Zyklusverlängerung durch einen "WAIT"-Takt eingeschoben werden.

Gebildet wird WAIT über die beiden FF A14, gesteuert durch die Signale TAKT und MT. Durch diese Schiebekette ist das Signal WAIT solange low, wie zur Einblendung eines TW-Taktes durch die ZRE nötig ist. Durch eine Open-Kollektor-Stufe A15/06 ist das Siganl auf den Bus geschaltet.

Die Adreßbits AB12 ... AB15, die auf der STE die Blockauswahl vornahmen, werden in Abhängigkeit der Programmierung der Anfangsadressierung durch die Brücken X9:1 ... X9:4; X10:1 ... X10:4 zur internen Adresse AB12K ... AB15K durch den Adderbaustein A13 umgerechnet. Die Funktionsweise dieses Adderbausteins T 183 ist aus Punkt 6.4.2.2. zu ersehen. Das Freigabesignal für den 1 aus 8-Decoder A10 wird nur gebildet, wenn die Adreßbits AB14K und AB15K O-Potential besitzen. Dann adressieren die Bit AB12K und AB13K die Speicherblöcke der STE.

Die Prioritätenketten BAT; BAO

IEI; IEO

IEIT; IEOT sind auf der Steckeinheit nur gebrückt.

Kurz- und langseitige Störungen auf der Betriebsspannung werden durch Sieb- und Stützkondensatoren gesiebt.

#### Beachte!

Aufgrund der spezifischen dynamischen Eigenschaften der dynamischen RAM-Bausteine (Störbeeinflussung) ist die Speichersteckeinheit K 3525 in der Nähe der ZRE und in Systemen mit Buserweiterung mittels Busverstärker BVE im Primärbus anzuordnen.

## 6. Programmierbarer Festwertspeicher PFS K 3820

## 6.1. Kurzcharakteristik

Mit Hilfe des programmierbaren Festwertspeichers PFS K 3820 ist es möglich, nicht variable Daten (Festdaten) zu speichern. Ein Datenerhalt ist auch nach Abschaltung bzw. Ausfall der Betriebsspannungen gewährleistet. Auf der STE (Typ 012-7041) befindet sich ein 16 K-Byte großer programmierbarer Festwertspeicher (EPROM-Speicher) mit den Funktionsgruppen:

- Entkopplung (Ein- und Ausgabepuffer)

- zur Auswahl und Ansteuerung der Speicherbauelemente.

Die EPROM-Speicherchips sind über 24-polige DIL-Steckfassungen auf der Steckeinheit kontaktiert. Das Programmieren der EPROM-Schaltkreise erfolgt außerhalb der STE auf einem EPROM-Programmiergerät. Eine Änderung der gespeicherten Leseinforamtionen ist nur mittels Programmiergerät möglich.

## 6.2. Technische Daten

Speicherkapazität:

Speicherschaltkreistyp:

Zugriffszeit:

Betriebsart:

Datenerhalt:

Stromversorgung:

16 K Byte (Anordnung von 16 Speicherchips)

Q 260

1 K x 8 Bit; nMOS

≤ 350 ns

"Lesen" als abgeschlossener Zyklus (Programmieren und Löschen der Speicherbauelemente ist nur extern

mit Programmiergerät möglich).

Ist auch nach Abschaltung bzw. Ausfall der Betriebsspannung gewährleistet.

$5 P = 5 V \pm 5 \%, \le 0.9 A$

$5 N = -5 V \pm 5 \%, \le 0.5 A$   $12 P = 12 V \pm 5 \%, \le 0.9 A$

Beachte!

Die Spannung 5 N darf nicht später als 10 ms nach Zuschalten von 5 P bzw. 12 P ihren Nennwert erreichen und höchstens 10 ms vor Wegfall der 5 P bzw. 12 P abschalten.

## 6.3. Programmierung der Steckeinheit

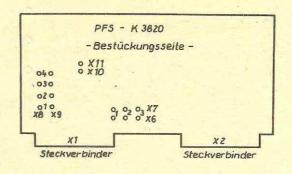

#### 6.3.1. Programmierfelder der Steckeinheit

Die Auswahlfelder bestehen aus Wickelstiftpaaren oder Mikroschaltern. Im ersteren Fall erfolgt die Codierung durch das Wickeln von Brücken.

Abb. 6

## 6.3.2. Adressenzuordnung

Die 16 Adreßleitungen des Systembusses haben folgende Zuordnung:

ABO ... AB9 - interne Chipadressierung

AB12 ... AB15 - Durch Umschlüsselung wird im Speicher die Adresse AB12K ... AB15K wirksam. Sie ergibt sich aus der stellenrichtigen Subtraktion der im Programmierfeld X8-X9 ausgewählten Anfangsadresse der STE und der angelegten Adresse AB12 ... AB15.

AB10, AB11 - Auswahl einer der 16 1 KByte-Blöcke der STE (Chipauswahl)

AB14K, AB15K - STE wird ausgewählt, wenn beide Signale 0-Potential besitzen

## Festlegung der Anfangsadresse der STE:

Die 4 Wickelbrücken bzw. Schalter erhalten in binärer Verschlüsselung die Anfangsadresse der STE innerhalb des Gesamtspeichers des MR. Die Programmierung erfolgt durch entsprechende Brücken des Programmierfeldes X8:1 ... X8:4, X9:1 ... X9:4. Diese Adresse ist ein ganzzahliges Vielfaches von 4 K.

|                                     |             | Wickelb     | rücken      |             |

|-------------------------------------|-------------|-------------|-------------|-------------|

| Adrebbereich                        | X8:4 - X9:4 | X8:3 - X9:3 | X8:2 - X9:2 | X8:1 - X9:1 |

| 0000 - 3FFF                         | -           |             | 7 64 0      | <u></u>     |

| 1000 - 4FFF                         | -           | -           | -           | Brücke      |

| 2000 - 5FFF                         |             |             | Briicke     |             |

| 3000 - 6FFF                         | _           |             | Brücke      | Brücke      |

| 4000 - 7FFF                         | -           | Brücke      | _           | -           |

|                                     |             |             |             |             |

| COOO - FFFF                         | Brücke      | Brücke      | -           | -           |

| Wertigkeit<br>der Wickel-<br>brücke | ≙ 32 K      | ≙ 16 K      | ≙ 8 K       | = 4 K       |

## 6.3.3. Belegung der EPROM-Bauelemente auf der STE

Die programmierten EPROM-Bauelemente befinden sich auf DIL-Steckfassungen. Die Belegung geht aus Abb. 7 hervor. Es ist aber zu beachten, daß die in der Abbildung genannten Adressen relativ zur programmierten Anfangsadresse der STE zu werten sind.

| 3000 - 33FF | 3400 - 37FF | 3800 - 3BFF | 3000 - 3FFF          |

|-------------|-------------|-------------|----------------------|

| 2000 - 23FF | 2400 - 27FF | 2800 - 2BFF | 2 <b>0</b> 00 - 2FFF |

| 1000 - 13FF | 1400 - 17FF | 1800 - 1BFF | 1000 - 1FFF          |

| 0000 - 03FF | 0400 - 07FF | 0800 - OBFF | OCOO - OFFF          |

| L           |             |             |                      |

Abb. 7

## 6.3.4. Auswahl des Speichersperrsignals MEMDI

|         |          | Wickelbrücken |             |             |  |  |  |  |  |  |

|---------|----------|---------------|-------------|-------------|--|--|--|--|--|--|

| Signal  |          | X6:1 - X7:1   | X6:2 - X7:2 | X6:3 - X7:3 |  |  |  |  |  |  |

| MEMDI   | (X1:B09) | Brücke        |             |             |  |  |  |  |  |  |

| MEMDI 1 | (X2:A21) |               | Brücke      | -           |  |  |  |  |  |  |

| MEMDI2  | (X2/B21) |               |             | Brücke      |  |  |  |  |  |  |

Bei Verwendung von Schaltern entspricht "Brücke" dem geschlossenen Schalter.

## 6.3.5. Bildung von "WAIT"

Von der Zugriffszeit der verwendeten Speicherbauelemente hängt es ab, ob während des Befehlszyklus im MR eine Zeitverlängerung über "WAIT" vorgenommen werden muß. Es gilt folgendes:

- Bildung von "WAIT" im M1-Zyklus: Brücke X10-X11 offen

- keine "WAIT"-Bildung:

Brücke X10-X11 geschlossen

#### 6.4. Funktionsbeschreibung

## 6.4.1. Verwendungszweck

Der PFS K 3820 wird im Erzeugnisprogramm "Dezentrale Datentechnik" als programmierbarer Festwertspeicher (nur Lese-Speicher) eingesetzt und erhält feste Programme oder Daten.

#### 6.4.2. Funktion

# 6.4.2.1. Funktionsbeschreibung

Auf der Steckeinheit befinden sich folgende Funktionsgruppen:

- Speichermatrix

- Ein- und Ausgabepuffer

- Auswahlelektronik

- Steuerelektronik

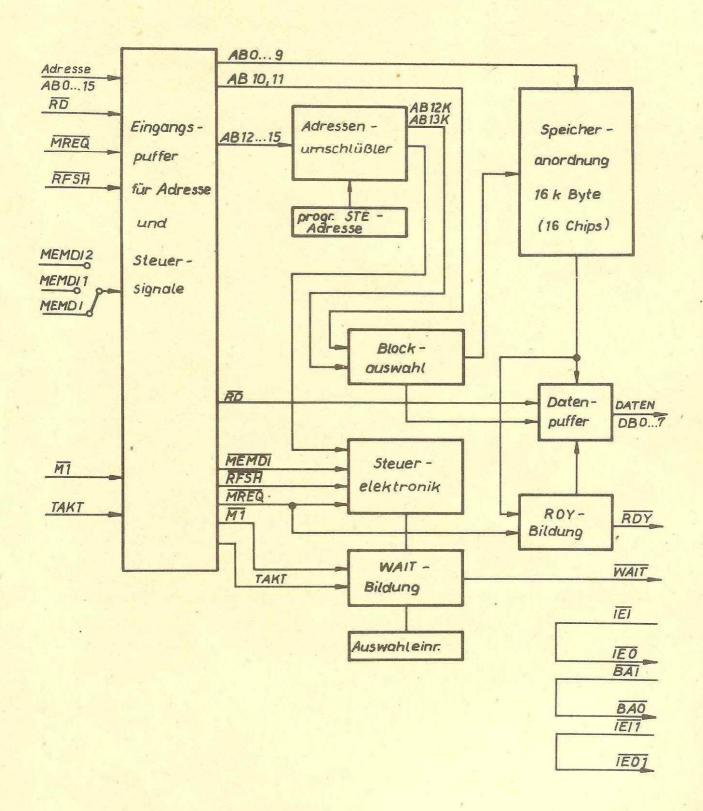

Die Wirkungsweise der Schaltung ist aus dem Blockschaltbild (Abb. 8) zu ersehen. Die Speichermatrix besteht aus 16 Speicherbausteinen Q 260 zu je 1 K Byte Speicherkapazität.

Die Adreßeingänge ABO ... AB9 liegen parallel an allen Eingängen der Speicherchips an, sie werden über Schottky-TTL-Pufferschaltkreise SE12 (A2/3) verstärkt. Die Datenausgänge DOO ... DO7 sind ebenfalls parallelgeschaltet und über die Datenpufferschaltkreise SE16 (A7/8) auf den Systembus geführt. Diese Ausgänge sind "Tri-state"-Ausgänge.

Die Auswahl und der Aufruf der 1 K-Speicherbereiche erfolgt über 16  $\overline{\text{CS}}$ -Signale. Liegt ein Speicheraufruf vor, wird über zwei 1 aus 8-Decoder SE05 (A5, A14) eines der 16  $\overline{\text{CS}}$ -Signale aktiv mit low. Der adressierte Speicherplatz wird gelesen.

Die Umcodierung der über den Bus angelegten Adreßbits AB12 ... AB15 wird durch den Adder⇒ baustein PS83 vorgenommen (siehe Punkt 6.4.2.2.).

Dieser Adderbaustein A1 verknüpft die angelegte Adresse AB12 ... AB15 mit der im Auswahlfeld codierten Bereichsanfangsadresse. Es entstehen am Ausgang die internen STE-Adressen

AB12K ... AB15K.

Die Adresbits AB10, AB11 und die umcodierten Bits AB12K und AB13K (FO/F1) bilden durch den Decoder SE05 A5/A14 die Auswahlsignale CS1 ... CS16 der Speicherchips, vorausgesetzt, die Ausgänge des Adderbausteins AB14K und AB15K (F2/F3) geben die Decoder über das Nand A12 frei (MEMDI und RFSH = high).

Gleichzeitig wird mit dem Freigabesignal (A12/6 = 0) über das Nand A12/8  $\overline{\text{CS}}$  = low für die Datenpuffer A7/8 gebildet und die Daten aus dem Speicher auf den Bus geschaltet. Das Netzwerk für die Bildung des Steuersignals "WAIT" wird ebenfalls freigegeben (Eingang R (A10) = high). Ist die Brücke X10-X11 nicht gesetzt, wird aus der mit den Signalen M1 und TAKT gesteuerte Schiebekette aus 2 FF A10 das WAIT = low aktiv abgeleitet und über die Open-Kollektor-Baustufe A13 auf den Bus geschaltet.

Die Bildung des Signals RDY wird bei den Festwertspeichern vom Datenausgang der Speicherchips abgeleitet. Das hat den Vorteil, daß das Signal neben der Aufrufbestätigung der STE auch eine Aussage über das hardwaremäßige Vorhandensein des adressierten ROM-Speicherchips bringt. Ausgewertet wird, ob die Datenleitung einen gültigen Logikpegel hat oder ob der hochohmige "Tri-state"-Zustand vorliegt. Dazu reicht aus, wenn ein Datenbit durch die Komperatorschaltung AS10 (A11) bewertet wird.

Liegt der hochohmige Zustand vor, werden die Spannungspegel an den Eingängen des Komperators so eingestellt (durch die zwei Spannungsteiler), daß der Ausgang A11/09 low ist. Bei einem gelesenen Logikpegel auf der Datenleitung werden die Potentiale an den Spannungsteilern über die Eingangsdioden so verändert, daß am Eingang eine positive Steuerspannung entsteht. Der Ausgang wird high und bildet RDY = low (aktiv).

Zur Durchschaltung der Prioritätenketten für die Unterbrechungsbearbeitung und für die Busherrschaft im Systembus werden die Klemmen: IEI, IEO

BAI, BAO

IEIT, IEOT miteinander gebrückt.

Kurz- und langzeitige Störungen auf den Betriebsspannungen 5 P, 5 N und 12 P sind durch Folien- und Elektrolytkondensatoren abgeblockt.

## 6.4.2.2. Adresdecodierung durch 4 Bit Volladder PS83

Über den 4 Bit Volladder SN 7483 (≘ T 183) erfolgt die Adreßdecodierung für die Auswahl der ROM-Chips dieses Festwertspeichers. Die Eingänge AO, A1, BO, B1 und CO werden verknüpft zu FO, F1 und dem Halbbyteübertrag C2. A2, A3, B2, B3 und C2 führen zu F2, F3 und C4. Der Ausgang C4 ist in diesem speziellen Fall der Speicher-STE nicht angeschlossen.

| - Control - Cont |       |    |     |     |   |                     |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|-----|-----|---|---------------------|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C4 14 | 02 |     |     | = | interner Übertrag   |   |

| 11 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FO 09 | CO |     |     | = | Übertrageingang     |   |

| _08 A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61 06 | C4 | *   |     | = | Übertragausgang     |   |

| 07 B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | FO |     | F3  | = | Summenausgänge      |   |

| 06 R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | F2 02 | AO |     | A.3 | = | Eingangsbit Summand | A |

| . 01 A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52 15 | ВО | 000 | В3  | = | Eingangsbit Summand | В |

| <del>- 16</del> 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13    |    |     |     |   |                     |   |

# Wahrheitstabelle

| ſ |    |    |    |    |    |    |    |    | -  |    |    | C2 | = ( | )  | 02 | = ' | 1  |

|---|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|-----|----|

| 1 | AO | ВО | A1 | B1 | FO | F1 | 02 | A2 | B2 | A3 | В3 | F2 | F3  | C4 | F2 | F3  | C4 |

| T | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 1  | 0   | 0  |

| 1 | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 0   | 0  | 0  | 1   | 0  |

|   | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0   | 0  | 0  | 1   | 0  |

|   | 1. | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1   | 0  | 1  | 1   | 0  |

|   | 0. | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1   | 0  | 1  | 1   | 0  |

|   | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 1   | 0  | 0  | 0   | 1  |

|   | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1   | 0  | 0  | 0   | 1  |

|   | 1  | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0   | 1  | 1  | 0   | 1  |

| 1 | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1   | 0  | 1  | 1   | 0  |

|   | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 1   | 0  | 0  | 0   | 1  |

| 1 | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1   | 0  | 0  | 0   | 1  |

|   | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 0   | 1  | 1  | 0   | 1  |

|   | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0   | 1  | 1  | 0   | 1  |

|   | 0  | 1  | 1  | 1  | 0  | 1  | 1. | 0  | 1  | 1  | 1  | 1  | 0   | 1  | 0  | 1   | 1  |

|   | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0   | 1  | 0  | 1   | 1  |

|   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1   | 1  | 1  | 1   | 1  |

Abb. 8 Blockschaltbild K 3820