### IX.

### Technische Beschreibung

Speichereinheiten OPS - K 3520

PFS - K 3820

OFS - K 3620

### Inhaltsverzeichnis

|        |                                        | Seite          |

|--------|----------------------------------------|----------------|

| 1.     | Allgemeine Beschreibung                | IX-4           |

| 1.1.   | Allgemeine technische Daten            | IX-4           |

| 1.2.   | Speicherorganisation                   | IX-4           |

| 1.3.   | Anschlußbedingungen der Speichermoduln | IX-5           |

| 2.     | Operativapeicher OPS K 3520            | IX-9           |

| 2.1.   | Kurzcherakteristik                     | <b>IX-</b> 9   |

| 2.2.   | Spezifische technische Daten           | I <b>X-</b> 9  |

| 2.3.   | Programmierung der Steckeinheit        | IX-10          |

| 2.3.1. | Programmierfelder der Steckeinheit     | IX-10          |

| 2.3.2. | Adressenzuordnung                      | I <b>X-1</b> 0 |

| 2.3.3. | Auswahl des Speichersperrsignals MEMDI | IX-11          |

| 2.3.4. | "WAIT"-Generierung                     | IX-12          |

| 2.3.5. | Betriebsspannungszuführung 5 PG        | IX-12          |

| 2.4.   | Funktionsbeschreibung                  | IX-12          |

| 2.4.1. | Verwendungszweck                       | IX-13          |

| 2.4.2. | Funktion                               | IX-13          |

| 3.     | Programmierbarer Festwertspeicher      | I <b>X-1</b> 7 |

|        | PFS K 3820                             |                |

| 3.1.   | Kurzcharakteristik                     | IX-17          |

| 3.2.   | Spezifische technische Daten           | IX-17          |

| 3.3.   | Programmierung der Steckeinheit        | IX-18          |

| 3.3.1. | Programmierfelder der Steckeinheit     | IX-18          |

| 3.3.2. | Adressenzuordnung                      | IX-19          |

| 3.3.3. | Plazierung der ROM-Elemente auf der    | IX-20          |

|        | Steckeinheit                           |                |

| 3.3.4. | Auswahl des Speichersperrsignals MEMDI | IX-20          |

| 3.3.5. | "WAIT"-Generierung                     | IX-21          |

| 3.4.   | Funktionsbeschreibung                  | IX-21          |

| 3.4.1. | Verwendungszweck                       | IX-21          |

| 3.4.2. | Funktion                               | IX-21          |

|        |                                                     | Seite          |

|--------|-----------------------------------------------------|----------------|

| 4.     | Operativ-/Festwertspeicher OFS K 3620               | IX-25          |

| 4.1.   | Kurzcharakteristik                                  | I <b>X-</b> 25 |

| 4.2.   | Spezifische technische Daten                        | IX25           |

| 4.3.   | Programmierung der Steckeinheit                     | IX-27          |

| 4.3.1. | Programmierfelder der Steckeinheit                  | IX-27          |

| 4.3.2. | Adre ssenzuordnung                                  | IX-27          |

| 4.3.3. | Vertauschung der RAM/ROM-Bereiche                   | IX29           |

| 4.3.4. | Plazierung der ROM-Elemente auf der<br>Steckeinheit | I <b>X-</b> 29 |

| 4.3.5. | Auswahl des Speichersperrsignals MEMDI              | IX-30          |

| 4.3.6. | "Wait"-Generierung                                  | IX-31          |

| 4.3.7. | Betriebsspannungszuführung 5PG                      | IX-31          |

| 4.4.   | Funktionsbeschreibung                               | IX-31          |

| 4.4.1. | Verwendungszweck                                    | IX-31          |

| 4.4.2. | Funktion                                            | I <b>X-</b> 32 |

### 1. Allgemeine Beschreibung

### 1.1.

### Allgemeine technische Daten

Steckeinheitenabmessungen: 215 mm x 170 mm

Steckraster:

20 mm

Steckverbinder:

2 x 58polig, indirekt, Bauf. 304-58

TGL 29331/03 bzw.

2 x 58polig, direkt

TGL 29331/01

Einsatzklasse:

5/60/30/95/10-1<sub>R</sub>

Be triebsspannung:

5₽ 4 5 V

5N 4 - 5 V

5 PG 4 5 V

12 P △ 12 V

Siehe dazu spezifische technische Daten des jeweiligen Speichermoduls.

### 1.2. Speicherorganisation

Für die Adressierung des Speichers des Mikrorechners K 1520 stehen 16 Adresbits zur Verfügung. Das erlaubt, max. 64K Byte Speicherzellen wahlfrei zu adressieren.

Durch Schaltmaßnahmen außerhalb der Moduln des K 1520 kann unter Benutzung der Signalleitungen /MEMDI1 und /MEMDI2 auf dem Koppelbus die Speicherkapazität erweitert werden. Die Aufrufbreite beträgt 8 Bit. Die Speicherkapazität kann je nach Erfordernis des Gesamtgerätes durch den wahlweisen Einsatz von Festwert- und Schreib-Lese-Speichern realisiert werden. Es steht ein Sortiment von Speichermoduln zur Verfügung, aus dem der Speicher bis zur adressierbaren Kapazitätsgrenze in beliebiger Kombination aufgebaut werden kann. Allen Speichermoduln können entsprechend des Speichervolumens über Programmiereinrichtungen auf den Steckeinheiten (Wickelbrücken oder Schalter) zusammenhängende Adreßbereiche zugeordnet werden, wobei die Speicheranfangsadressen ganzzahlige Vielfache von 4K bilden. Damit ist es möglich, geschlossene Speicherfelder zu erzielen und sie den Erfordernissen der Programmsysteme anzupassen. Adressen dürfen dabei nicht mehrfach belegt werden. Das ist im Adreßbereich von ØØØØ bis ØFFF besonders zu beachten. Dann sind diese Adressen auf den ZRE-Steckeinheiten K 2521 ... K 2524 einem 4K-Speicher fest zugeordnet.

Die Speichersteckeinheiten werden ein- und ausgangsseitig auf dem BUS parallel geschaltet. Demit ergibt sich ein steckplatz- unabhängiger Einestz der Speichersteckeinheiten.

Alle die Speicher berührenden Adreß-, Daten- und Steuerleitungen des Busses sind durch Pufferschaltkreise mit Low-Power-Schettky-Eingängen von den Steuer- und Speicherschaltkreisen entkoppelt. Die Pufferschaltkreise der Datenleitungen arbeiten bidirektional und besitzen einen "Tri-state"-Zustand. Die auf den Speichersteckeinheiten erzeugten Steuersignale werden über Open-Kollektor-Baustufen ausgesendet.

Zur Geschwindigkeitssynchronisierung zwischen Prozessor und Speicher sind die Speichersteckeinheiten mit einer "WAITE Steuerng" ausgerüstet.

Ein Quittierungssignal "RDY" wird ausgesendet, wenn eine ausgewählte Steckeinheit einen gültigen Lese- oder Schreibaufruf erhält und ein Datenaustausch vorgenommen wird.

# 1.3. Anschlußbedingungen der Speichermoduln

- Signalpegel: Low-Potential: Eingänge - 1,0 ...+0,85 V

Ausgänge 0 ...+0,45 V

High-Potential: Eingänge + 2,0 ...+ 5,5 V

Ausgänge + 2,4 ...+ 5,5 V

### - Signalbelastung:

Alle von den Speichersteckeinheiten empfangenen Signale (Adreß- und Steuerbits, Dateneingang) werden mit max. 0.25 må belastet.

Der Datenausgang ist mit 15 TTL-Lasteinheiten (24 mA) belastbar.

Die Open-Kollektor-Ausgänge der Steckeinheiten treiben max.

10 TTL-Lasteinheiten (16 mÅ), wobei sich im Lastkreis außerhalb der Steckeinheit jeweils mindestens ein Lastwiderstand

befinden muß.

### - Von Speichermoduln empfangene Signale:

Adresse - 16 Bit, ABO ... AB15

Die niederwertigen Bits ab ABO dienen der internen Adresentschlüsselung in den Speicherchips, nachfolgende Bits entschlüsseln Adresgruppen auf den Steckeinheiten und die höchstwertigen Bits wählen die gewünschte Steckeinheit aus.

Daten - 8 Bit, DBO ... DB7

Binschreibende Daten bei "/RD" und "WR" auf

bidirektionalem Datenbus.

MRBQ - Speicheranforderungssignal, wirkt funktionell als Taktsignal für Speicher.

Aktiviert zeitbestimmend / CB-Bingänge der Speicherchips.

WR - Befehlssignal "Speicher schreiben"

Steuert die Arbeitsweise "Lesen" oder "Schreiben"

ben" der Speicherchips über deren Eingang /WE.

RD - Befehlssignal "Speicher lesen"

Bestimmt die Wirkungsrichtung der bidirektionelen Datenpuffer.

MEMDI,

MEMDI1,

MEMDI2

Be ist über Wickelbrücken oder Schalter wahlweise vom Systembus X1:B09 oder Koppelbus

X2:A21 (MEMDI1) bzw. X2:B21 (MEMDI2) zu empfangen.

Bedeutung der diesbezüglichen Wickelbrücken bzw. Schalter in der Reihenfolge:

1 geschlossen - MEMDI über X1:B09 empfangen

2 geschlossen - MEMDI1 über X2:A21 empfangen

3 geschlossen - MEMDI2 über X2:B21 empfengen Das Sperrsignal schaltet die Ausgengspuffer zum Datenbus in den "Tri-state"-Zustand und sperrt die /CE-Eingänge der Speicher. Dadurch können externe Geräte auf dem Bus verkehren, ohne die Speicher zu beeinflussen. Darüber hinaus wird eine zusätzliche Steuerung der Speicher in Abhängigkeit von Adreßbereichen bzw. zusätzlichen Adresbits möglich.

#### Betriebsarten:

- Normalkonfiguration bei max. Speicherkapazität bis 64K Byte: Brücke MEMDI geschlossen, MEMDI1 und MEMDI2 offen

- AdreBerweiterung unter Benutzung des Sperrsignals: Brücke MEMDI offen, MEMDI1 oder MEMDI2 je nach gewinschter Programmierung der STE geschlossen. Zusatzverdrahtung auf Koppelbus und Zusatz-

- Steuersignal für das Auffrischen dyn. RAM-Spei-RFSH char

elektronik erforderlich.

- Systemtakt und Kennzeichen "Befehlslesezyklus": TAKT. M1 Zur Auslösung eines "WAIT"-Zyklus während des Befehlslesezyklus (M1-Zyklus) erforderlich. "WALT"-Zyklus wird unterdrückt, wenn diesbezügliche Auswahleinrichtung auf der Steckeinheit gebrückt ist.

- Von Speichermoduln generierte Signale:

- 8 Bit, DBO ... DB7 Daten Aus Speicher gelesene Daten bei RD und /WR auf bidirektionalem Datenbus.

WAIT - Signal löst "WAIT"-Zyklus im Prozessor aus.

Dies wird erforderlich, wenn die Zykluszeit des

Speichers größer als die Zeitdauer des Befehlslesezyklus ist.

RDY - Quittierungssignal. Wird ausgesendet, wenn auf betreffender Speichersteckeinheit eine adressierte Speicherzelle hardwaremäßig vorhanden ist und zum Datenaustausch zur Verfügung steht.

### - Ansteuerbedingungen:

Die dyn. Kennwerte der Speichermoduln sind auf das Signalspiel des gemeinsamen Bussystems des MR K 1520 abgestimmt. Folgende allgemeine Bedingungen sind zu gewährleisten: Die Adresse muß mindestens 530 ns am Bus stabil anliegen. MREQ erscheint 140 bis 240 ns nach Anlegen der gültigen Adresse und bleibt bis Adreßwechsel aktiv. Es muß debei mindestens 300 ns vor Schreibimpulsende WR gültig sein und bis zu dessen Ende anliegen, wenn der Speicher beschrieben wird.

Der Schreibimpuls WR selbst muß spätestens 300 ns vor dem folgenden Adreßwechsel anliegen und bis zum Adreßwechsel gültig sein. Beim Lesen erscheint RD spätestens 170 ns nach Adreßwechsel und bleibt mindestens bis Ende MREQ aktiv. M1 wird wie die Adresse geschaltet.

Zu schreibende Daten müssen mindestens 300 ns vor Abschalten von WR bis zum Abschalten von WR anliegen.

Gelesene Daten sind spätestens 450 ns nach Adreswechsel gültig. Die Übernahme in Nachfolgeregister erfolgt kurz vor der Abschaltflanke von MREQ.

### 2. Operativspeicher OPS K 3520

#### 2.1.

### Kurzcherekteristik

Der Schreib-Lese-Speicher (Operativspeicher) OPS K 3520 dient zur Speicherung aller variablen Daten während des Programmablaufs im Mikrorechner K 3520.

Br wird durch den Steckeinheitentyp 012-7011 mit indirektem bzw. 012-7016 mit direktem Steckverbinder realisiert und beinhaltet einen 4K Byte großen statischen Halbleiterspeicher (nMOS-RAM) mit den zur Entkopplung, Auswahl und Ansteuerung erforderlichen bipolaren Schaltkreisen.

## 2.2. Spesifische technische Daten

| Speicherkapasität: | 4K Byte |

|--------------------|---------|

|--------------------|---------|

(Anordnung von 4 x 8 Speicherchips)

Speicherschaltkreistyp: Q240

1K x 1 Bit, nMOS

Zugriffzeit:

≤ 530 ns

Betriebearten:

"Lesen" oder "Schreiben" als

abgeschlossene Zyklen in beliebi-

ger Reihenfolge

Datenerhalt: Information geht bei Abschaltung

der Betriebsspannung verloren.

Bin Datenerhalt ist möglich, wenn

im Ruhezustand des Speichers eine

Spannung (Schlafspannung) von außen über Klemme 5PG zugeführt

wird. Diese Spannung muß 2 V sein.

$5P = 5 V \pm 5 \%$ , typisch 0,6 A

für Steuerelektronik und Puffer-

schaltkreise

5PG \* 5 V ± 5 %, typisch 1,1 A (bei 2 V Schlafspannung etwa 0,6 A) für Speicherschaltkreise

2.3.

Programmierung der Steckeinheit

2.3.1.

Programmierfelder der Steckeinheit

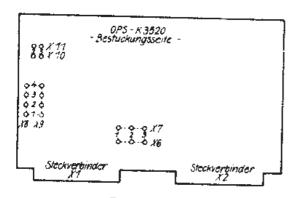

Abb. IX/1

Die Programmierfelder bestehen aus Wickelstiftpaaren oder Mikroschaltern. Im ersteren Fall erfolgt die Programmierung, indem Wickelstiftpaare in Wickeltechnik miteinander verbunden werden.

## 2.3.2. Adressenzuordnung

Die 16 Adressignale werden im Speichermodul wie folgt bewertet:

ABO ... AB9 - interne Chipadressierung

AB10, AB11 - Auswahl einer der 4 1K-Blöcke auf der STE

AB12 ... AB15 - Auswahl der Steckeinheit in Abhängigkeit von der Adressenzuordnung der Steckeinheit

Zuordnung des Adresbereiches der Steckeinheit:

Über 4 Wickelbrücken bzw. 4 Schalter X8:1 ... 4, X9:1 ... 4 wird dem Speichermodul ein wählbarer zusammenhängender Adres-bereich von 4K Adressen zugeordnet.

Das Programmierfeld erhält in binärer Verschlüsselung die Anfangsadresse des gewünschten Adresbereiches. Die Adresse ist ein ganzzahliges Vielfaches von 4K.

#### Kodetabelle:

| Wickelbrücken      |           |           |           |           |

|--------------------|-----------|-----------|-----------|-----------|

| Adresbereich       | X8:4-X9:4 | X8:3-X9:3 | X8:2-X9:2 | X8:1-X9:1 |

| 0000~0FFF          | -         | -         | -         | _         |

| 1000 <b>-1F</b> FF | -         | -         | -         | Brücke    |

| 2000-2 <b>FFF</b>  | <b>↔</b>  | ₩         | Brücke    | -         |

| 3000-3FFF          | -         | -         | Brücke    | Brücke    |

| 4000-4 <b>FFF</b>  | <b>→</b>  | Brücke    | -         | -         |

| • •                | •         | •         | •         | •         |

| • •                | •         | •         | •         | •         |

| • •                | •         | •         | •         | •         |

| FOOO-FFFF          | Brücke    | Brücke    | Brücke    | Brücke    |

Bei Schalterbestückung entspricht "Brücke" dem geschlossenen Schalter.

2.3.3.

Auswahl des Speichersperrsignals MEMDI

| chermodul | Wicke                           |                                              |                                 |

|-----------|---------------------------------|----------------------------------------------|---------------------------------|

| e Signale | X6:1-X7:1                       | X6:2-X7:2                                    | X6:3-X7:3                       |

| (X1:B09)  | Brücke                          | _                                            | -                               |

| (X2:A21)  | _                               | Brücke                                       | **                              |

| (I2:B21)  | -                               | -                                            | Brücke                          |

|           | Signale<br>(X1:B09)<br>(X2:A21) | Signale X6:1-X7:1 (X1:B09) Brücke (X2:A21) - | Signale   X6:1-X7:1   X6:2-X7:2 |

Bei Schalterbestückung entspricht "Brücke" dem geschlossenen Schalter.

## 2.3.4. "WAIT"-Generierung

Von den dynamischen Daten der aufgerufenen Speicherschaltkreise hängt es ab, ob während des Befehlslesezyklus im K 1520 eine Zeitverlängerung über "WAIT" vorgenommen werden muß. Durch die konkrete Bestückung der Steckeinheit ist bereits vorgegeben, wie die Einstellung erfolgen muß.

Für den allgemeinen Anwendungsfall kann die Einstellung wie folgt vorgenommen werden:

Generierung von "WAIT" im M1-Zyklus: Brücke X10:3-X11:3 offen Unterdrückung der "WAIT"-Bildung: Brücke X10:3-X11:3 ge-schlossen.

## 2.3.5. Betriebsspannungszuführung 5PG

Normalerweise werden die RAM-Speicherbausteine über den Betriebsspannungsanschluß 5PG versorgt. In Sonderfällen, wo die Anschlüsse 5PG auf dem Bus nicht belegt sind, kann 5PG steckeinheitenseitig durch die Brückung der Wickelstifte X10:2-X11:2 mit 5PG verbunden werden.

# 2.4. Funktionsbeschreibung

#### 2.4.1.

#### Verwendungesweck

Der OPS K 3520 wird im Mikrorechner K 1520 als Operativspeicher (statischer Schreib-Lese-Speicher) eingesetzt.

### Punktion

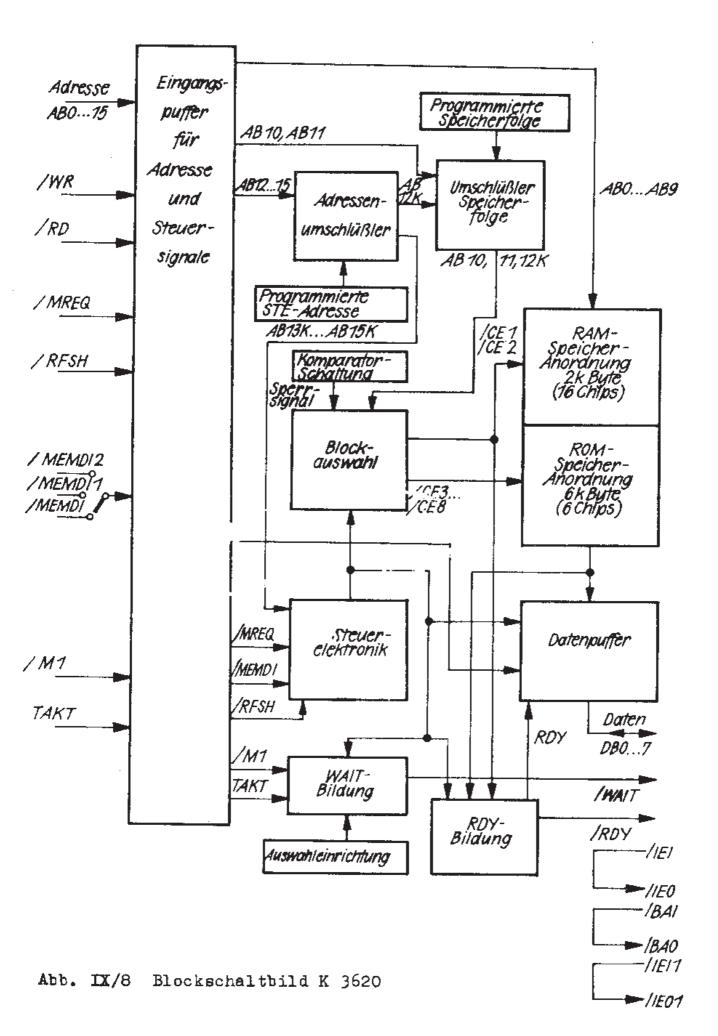

Die Steckeinheit beinhaltet die Funktionsgruppen Speicher-Matrix. Ein- und Ausgabepuffer und Auswahl- und Steuerelektronik. Die Wirkungsweise der Schaltung ist im Blockschaltbild Abb. IX/2 dargelegt.

Die Speichermatrix besteht aus 4 Gruppen zu je 8 Speicherchips Q240. Jedes Chip enthält 1K Bit, Eine Gruppe von 8 Chips bildet einen Speicherbereich von 1K Byte. Jede der 4 vorhandenen Chipgruppen wird durch ein gesondertes/CE-Signal aktiviert.

Alle 10 gleichnamigen Adreßeingänge und der Steuereingeng /WE (Schreib-Lese-Steuerung) der Speicherchips sind miteinender verbunden und werden von den entsprechenden Bussignelen über Schottky-TTL-Pufferschaltkreise SE12 gespeist.

Bei den Datenein- und Ausgangsleitungen sind jeweils die gleichen Bits der 4 Chipgruppen parallelgeschaltet und mit bidirektional arbeitenden Datenpufferschaltkreisen SE16 verbunden, die die Verbindung mit dem Systembus herstellen. Befindet sich die Steckeinheit im Ruhezustand, sind die Datenpuffer hochohmig und beeinflussen das Interfacespiel auf dem Systembus nicht.

Die ebenfalls über SE12 verstärkten Adreßsignale AB10 und AB11 werden im 1 aus 8-Dekoder-Baustein SE05 umkodiert und aktivieren eins der 4 Speicheransteuersignale /CE, wenn gleichzeitig das Anforderungssignal MREQ anliegt, das Speichersperrsignal MEMDI nicht aktiv ist (/MEMDI), kein Refresh-Zyklus vorliegt (/RFSH) und die Steckeinheit durch die gepufferten Adreßsignale

AB12 bis AB15 entsprechend der Adressenzwordnung ausgewählt wurde.

Der Exklusiv-Oder-Baustein PS86 übernimmt die Adressenumschlüsselung in Abhängigkeit vom Programmierfeld X8-X9. Bin

geschlossener Schalter bzw. gebrücktes Wickelstiftpaar ergibt

ein Nullsignal am zugehörigen Exklusiv-Oder-Eingang. Diese

Null bewirkt eine unnegierte Weiterleitung des zugeordneten

Adreßbits zur Auswerteschaltung. Bei High-Signal erfolgt eine

Negation des Adreßbitpotentials. Nur bei einer bestimmten Wertigkeit der Adreßbits AB12 bis AB15 bezüglich der Belegung der

Wickelbrücken wird die Steckeinheit angesprochen. In diesem

Falle sind alle 4 Eingänge der Auswerteschaltung auf "High"Potential.

Wird ein /CE-Signal freigegeben, werden ebenfalls die Datenpuffer zum Datenaustausch aktiviert, wobei RD die Wirkungsrichtung vorgibt, wird das Kennungssignal RDY erzeugt und

die Blockierung des "WAIT"-Bildungs-Netzwerks aufgehoben, sofern die Auswahlbrücke X10:3-X11:3 nicht gesetzt ist. So kann

beim Befehlslesen ein "WAIT"- Zyklus eingeschoben werden.

WAIT wird von einer Schiebekette aus 2 D-Flip-Flops abgeleitet, die mit dem Kennsignal M1 und dem Systemtakt TAKT gesteuert wird. Durch Einsatz von Open-Kollektor-Baustufen für

WAIT und RDY wird durch ausgangsseitiges Zusammenschalten auf

dem Systembus eine "Oder"-Funktion realisiert.

Zur Durchschaltung der Prioritätenkette auf dem Bus des K 1520 werden die Klemmen /IEI, /IEO, /IEI1, /EO1 und /BAI, /BAO auf der Steckeinheit jeweils miteinander gebrückt.

Um bei allgemeiner Netzausschaltung am Mikrorechner K 1520 einen Datenerhalt der Speicherschaltkreise durch externe Stützung der Betriebsspannung zu ermöglichen, ist die Strom-versorgung der Steckeinheit in zwei Kreise aufgeteilt. Über Klemme 5PG werden die Speicherchips gespeist. Ein Datenerhalt ist gesichert, wenn die Spannung 5PG im Ruhezustand des Speichers auf eine Schlafspannung von minimal 2 V abgesenkt wird.

Dabei kann die 5P für die Puffer-, Auswahl- und Steuerschaltkreise abgeschaltet werden. Damit im Zu- und Abschaltvorgang

der Spannung 5P keine undefinierten Ansteuerbedingungen am

Speicher wirksam werden können, die zum Datenverlust führen,

werden CE-Signale konjunktiv mit einem internen Speichersperrsignal verknüpft. Dieses Sperrsignal, gebildet in einer Komparatorschaltung, wird Null, sobald die Betriebsspannung 5P

die untere Toleranzgrenze unterschreitet. Damit ist sichergestellt, daß der Treiber PS26 in diesem Fall kein aktivierendes Ansteuersignal für die Speicher aussenden kann.

Über den mit der Spannung 5PGI verbundenen Arbeitswiderständen der Open-Kollektor-Treiberbaustufen wird auch im Schlafzustand der erforderliche "High"-Pegel am /CE-Eingang der Speicherchips aufrechterhalten.

Zur Abblockung von kurz- und langzeitigen Störungen auf den Betriebsspannungen 5P und 5PG sind (in der Leitungsführung verteilt) Stütz- und Sieb-Kondensatoren angeordnet.

#### 3.

### Programmierbarer Featwertspeicher PFS K 3820

### 3.1.

### Kurzcharakteristik

Der programmierbare Festwertspeicher dient der Speicherung von Festdaten für nichtvariable Programme u.g. innerhalb des Halbleiterspeichers K 1520.

Er wird durch den Steckeinheitentyp 012-7041 mit indirektem bzw. 012-7046 mit direktem Steckverbinder realisiert und beinhaltet einen 16K Byte großen programmierbaren Festwertspeicher (EPROM-Speicher) mit dem zur Entkopplung, Auswahl und Ansteueurung erforderlichen bipolaren Schaltkreisen.

Die EPROM-Schaltkreise sind über 24polige DIL-Steckfassungen auf der Steckeinheit kontaktiert. Das Beschreiben der EPROM-Schaltkreise erfolgt außerhalb der Steckeinheit auf einem EPROM-Programmiergerät. Eine Änderung der ROM-Leseinformation ist jederzeit durch Austausch oder Umprogrammierung der EPROM-Schaltkreise möglich.

## 3.2. Spezifische technische Deten

Speicherkapazität: 16K Byte

(Anordnung von 16 Speicherchips)

Speicherschaltkreistyp: Q260

1K x 8 Bit nMOS

Zugriffezeit: ≤ 530 ns

Betriebsarten: "Lesen" als abgeschlossener Zyklus

(Programmieren oder Löschen der Speicherbausteine ist nur extern mit Programmiergerät möglich).

Datenerhalt: Energieunabhängige Speicherung

von Festdaten

Stromversorgung:

$$5P = 5 V \pm 5 \%$$

, typ. 0,9 A

$5N = -5 V \pm 5 \%$ , typ. 0,5 A

$12P = 12 V \pm 5 \%$ , typ. 0,9 A

Es ist defür zu sorgen, daß die Spannung 5N nicht später als 10 ms nach Zuschaltung von 5P bzw. 12P ihren Nennwert erreicht und höchstens 10 ms vor Wegfall der 6P bzw. 12P abschaltet.

## 3.3. Programmierung der Steckeinheit

## 3.3.1. Programmierfelder der Steckeinheit

Abb. IX/3

Die Programmierfelder bestehen aus Wickelstiftpaaren oder Mikroschaltern. Im ersteren Fall erfolgt die Programmierung, indem Wickelstiftpaare nach der Wickeltechnik miteinander verbunden werden.

### 3.3.2.

#### Adressenzuordnung

Die 16 Adressignale werden im Speichermodul wie folgt bewertet:

ABO ... AB9 - interne Chipadressierung

AB12 ... AB15 - Umkodierung in Abhängigkeit von der im

Programmierfeld X8-X9 fixierten Adresse.

Die im Speicher wirksame Adresse AB12K ...

AB15K ergibt sich aus der stellenrichtigen

Subtraktion der in X8-X9 eingegebenen Steckeinheitenadresse von der angelegten Adresse

AB12 ... AB15.

AB10, AB11, - Auswahl einer der 16 1K Byte-Blöcke der STE (Chipauswahl)

AB14K, AB15K - Auswahl der Steckeinheit, wenn beide Signale Nullpotential besitzen.

Zuordnung des Adreßbereichs der Steckeinheit:

Über 4 Wickelbrücken bzw. 4 Schalter X8:1 ... 4, X9:1 ... 4 wird dem Speichermodul ein wählbarer zusammenhängender Adreß-bereich von 16K Adressen zugeordnet.

Des Programmierfeld erhält in binärer Verschlüsselung die Anfangsadresse des gewünschten Adreßbereiches.

Diese Adresse ist ein ganzzahliges Vielfaches von 4K.

### Kode tabelle:

|                   |           | Wickelbrücken |           |            |  |

|-------------------|-----------|---------------|-----------|------------|--|

| Adresbereich      | X8:4-X9:4 | X8:3-X9:3     | X8:2-X9:2 | X8:1-X9:1  |  |

|                   |           |               | _         | _          |  |

| 0000-3 <b>fff</b> | -         | ***           | _         | Double les |  |

| 1000-4 FFF        | 4-0       |               | -         | Brücke     |  |

| 2000-5 <b>FFF</b> | -         | _             | Brücke    | -          |  |

| 3000-6FFF         | -         | _             | Brücke    | Brücke     |  |

| 1000-7FFF         | -         | Brücke        | <b>-</b>  |            |  |

|                   | •         | •             | •         | •          |  |

| •                 | •         | •             | •         | •          |  |

| • •               | •         | •             | •         | •          |  |

| OOOO-FFFF         | Brücke    | Brücke        | **        | <b></b>    |  |

Bei Schalterbestückung entspricht "Brücke" dem geschlossenen Schalter.

3.3.3.

Plazierung der ROM-Elemente auf der Steckeinheit

Die programmierten ROM-Elemente werden über DIL-Steckfassungen auf der Steckeinheit kontaktiert.

Die einzelnen Steckplätze repräsentieren die im folgenden Schema dargestellten relativen Adreßbereich der Steckeinheit (bezogen auf die programmierte Steckeinheiten-Anfangsadresse).

| 3000 - 33 FF | 3400 - 37FF | 3800 - 3BFF | 3C00 - 3F   |

|--------------|-------------|-------------|-------------|

| 2000 - 23FF  | 2400 - 27FF | 2800 - 28FF | 2C00 - 2F)  |

| 1000 - 13FF  | 1400 - 17FF | 1800 - 18FF | 1000 - 1FF  |

| 0000 - 03FF  | 0400 - 07FF | 0800 - 0BFF | 0000 - 0FFF |

Abb. IX/A

3.3.4.

Auswahl des Speichersperrsignels MEMDI

| Im Speichermodul wirk-<br>semes Sperrsignal | X6:1-X7:1 | ckelbrücken<br>X6:2-X7:2 | X6:3-X7:3 |

|---------------------------------------------|-----------|--------------------------|-----------|

| MEMDI (X1:B09)                              | Brücke    | _                        | -         |

| MEMDI1 (X2:A21)                             |           | Brücke                   | <b></b>   |

| MEMDI2 (X2:B21)                             | -         | _                        | Brücke    |

Bei Schalterbestückung entspricht "Brücke" dem geschlossenen Schalter.

## 3.3.5. "WAIT"-Generierung

Von den dynamischen Deten der aufgerufenen Speicherschaltkreise hängt es ab, ob während des Befehlszyklus im K 1520 eine Zeit-verlängerung über "WAIT" vorgenommen werden muß.

Durch die konkrete Bestückung der Steckeinheit ist bereits vorgegeben, wie die Einstellung erfolgen muß.

Für den allgemeinen Anwendungsfall kann die Einstellung wie folgt vorgenommen werden:

Generierung von "WAIT" im M1-Zyklus: Brücke X10-X11 offen Unterdrückung der "WAIT"-Bildung: Brücke X10-X11 geschlossen.

### 3.4. Funktionsbeschreibung

### 3.4.1. Verwendungszweck

Der PFS K 3820 wird im Mikrorechner K 1520 als programmierbarer Festwertspeicher (Nur-Lese-Speicher) eingesetzt und erhält fixe Daten oder Programme.

## 3.4.2. Funktion

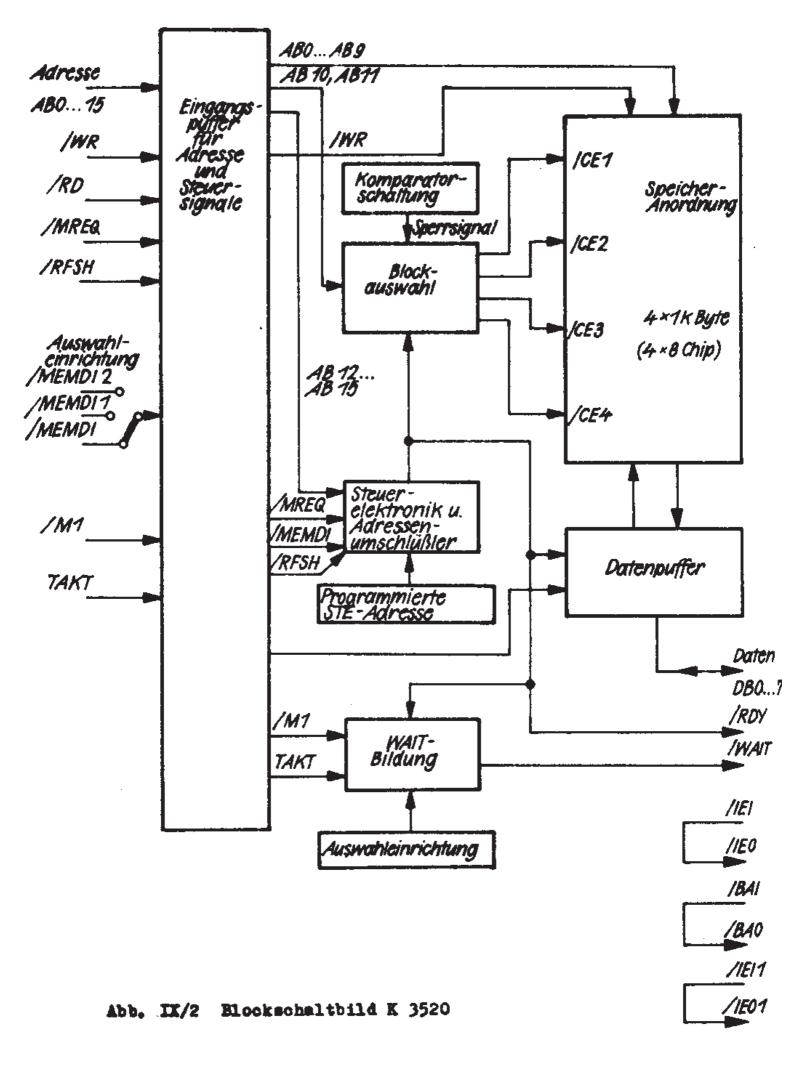

Die Steckeinheit beinhaltet die Funktionsgruppen Speichermatrix. Ein- und Ausgabepuffer und Auswahl- und Steuerelektronik.

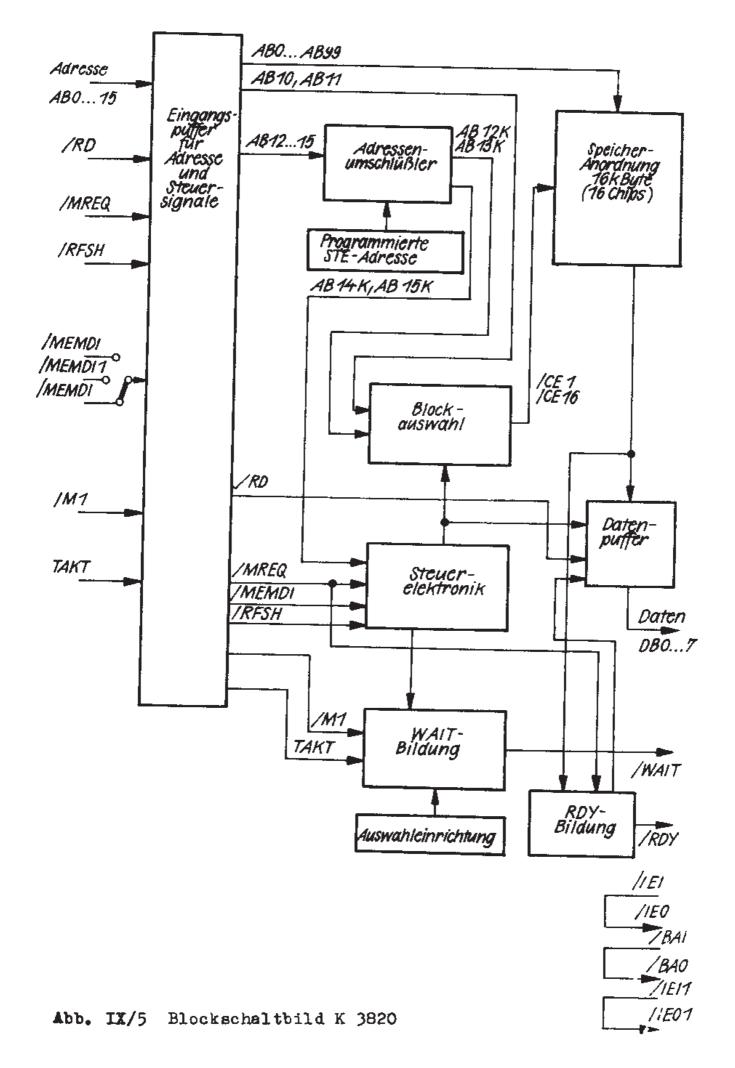

Die Wirkungsweise der Schaltung ist im blockschaltbild Abb. IX/5 dergelegt.

Die Speichermetrix bestent aus 16 Speicherbausteinen Q260 zu je 1K Byte à 8 Bit Speicherkapazität. Diese Bausteine sind auswechselbar auf DIL-Steckfassungen gesetzt.

Alle 10 gleichnemigen Adreßeingänge der Speicherchips sind miteinander verbunden und werden von den entsprechenden Bussignalen über Schottky-TTL-Pufferschaltkreise SE12 gespeist. Die gleichnamigen Datenausgänze sind ebenfalls parallelgeschaltet und mit den Datenpufferschaltkreisen SE16 verbunden, die die Lesedaten mit "Tri-State"-Ausgang an den Systembus abgeben.

Auswahl und Aufruf der 1K-Speicherbereiche, die durch separate Speicherbausteine realisiert werden, erfolgt über 16 /CE-Signa-1e, die zur "High"-Pegel-Erhöhung mit je einem Ziehwiderstend versehen sind.

Liegt ein Speicheraufruf vor, wird über ein Netzwerk aus zwei "1 aus 8"-Dekoderbausteinen SEO5 eines der /CE-Signale durch Nullsetzen aktiv. Ein Speicherplatz entsprechend angelegter Adresse wird gelesen.

Die Umkodierung der über den Bus angelegten vier höchsten Adrebbits wird durch einen Adderbaustein PS83 vorgenommen. Die Subtraktion: Angelegte Adresse AB12 ... AB15 minus in Programmierfeld eingegebene STE-Anfangsadresse (geschlossener Schalter = logisch "High"-Potential) wird technisch realisiert. indem das Zweierkomplement der Anfangsadresse im Baustein addiert wird. Als Ergebnis der Operation entsteht die echte interne Steckeinheitenadresse. Die Adrebbits AB10, AB11 und die umkodierten Bits AB12K und AB13K werden zur Speicherchip-Auswahl im Dekoder SE05 verwendet, während die umkodierten Bits AB14K und AB15K, wenn sie Nullpotential besitzen, zusammen mit MREQ, /RFSH und /MEMDI die Dekoder SE05 freigeben und damit die Steckeinheit auswählen und ektivieren. Bei progremmierter Leseoperation werden unter gleichen Bedingungen auch die Datenpuffer aktiviert, vorausgesetzt, ein "RDY"-Signel wurde auf Grund gültiger Leseinformation gebildet. Außerdem wird das "WAIT"-Bildungs-Netzwerk freigegeben. Ist die Brücke

X10-X11 nicht gesetzt, wird aus der mit "M1" und "Takt" angesteuerten Schiebekette aus 2 D-FF das "WAIT"-Signal abgeleitet und disjunktiv auf den Bus geschaltet.

Die Bildung des "RDY"-Signels wird bei den ROM-Speichern vom Datenausgang der Speicherchips abgeleitet. Das hat den Vorteil, daß das "RDY"-Signal neben der Aufrufbestätigung der Steckeinheit eine Aussage über das hardwaremäßige Vorhandensein des angesprochenen ROM-Speicherchips mit beinhaltet. Ausgewertet wird, ob die Datenleitungen einen gültigen Logikpegel besitzen oder ob der hochohmige "Tri-state"-Zustand vorliegt. Dazu reicht es aus, wenn ein Datenbit durch die Auswerteschaltung mit dem Komparatorbaustein AS10 bewertet wird.

Liegt der hochohmige Zustand vor, werden die Spannungspegel an den zwei Eingängen des Komparators durch die zwei Spannungsteiler so eingestellt, daß am Komparatorausgang, und damit für RDY, ein Nullsignel entsteht. Bei "Low"- oder "High"-Potential auf der Datenleitung werden die Potentiale an den Spannungsteilern über die zwei Eingangsdioden so verändert, daß der nichtnegierende Eingang des Komparators gegenüber dem negierenden eine positive Spannung annimmt. Der Bausteinausgang schaltet dabei auf "High"-Potential. Dieses Signal wird disjunktiv als RDY auf den Bus gelegt.

Bine in die Schaltung einbezogene gesteuerte Open-Kollektor-Baustufe beschleunigt beim Übergang der Datenleitung in den hochshmigen Zustand die Umladung der Kapazitäten und verbessert somit das dynamische Verhalten des Signals RDY.

Zur Durchschaltung der Prioritätenketten auf dem Bus des K 1520 werden die Klemmen /IEI, /IEO, /IEI1, /IEO1 und /BAI, /BAO auf der Steckeinheit jeweils miteinander gebrückt.

Zur Abblockung von kurz- und langzeitigen Störungen auf den Betriebsspannungen 5P, 5N und 12P sind (in der Leitungsführung verteilt) Stütz- und Sieb-Kondensatoren angeordnet.

Operativ-/Festwertepeicher OFS K 3620

#### 4.1.

### Kurzcharekteristik

Der kombinierte Schreib-Lese-Speicher (Operativspeicher) und programmierbare Festwertspeicher OFS K 3620 dient der Speicherung von variablen sowie Festdaten innerhalb des Halbleiterspeichers K 152 O. Dieser Speichermodul ermöglicht in der Kombination mit den anderen Speichermoduln eine Flexibilität in der Zusammensetzung der Halbleiterspeicher und realisiert ökonomisch kleine Speicher. Der OFS K 3620 wird durch den Steckeinheitentyp 012-7031 mit indirektem bzw. 012-7036 mit direktem Steckverbinder realisiert und beinhaltet einen 2K Byte großen statischen Halbleiterspeicher (nMOS-RAM) und einen 6K Byte großen programmierbaren Festwertspeicher (EPROM) mit den zur Entkopplung, Auswahl und Ansteuerung erforderlichen bipolaren Schaltkreisen.

Die EPROM-Schaltkreise sind über 24polige DIL-Steckfassungen auf der Steckeinheit kontaktiert.

Das Beschreiben der EPROM-Schaltkreise erfolgt außerhalb der Steckeinheit auf einem EPROM-Programmiergerät. Eine Änderung der ROM- Leseinformation ist jederzeit durch Austausch oder Umprogrammierung der PROM-Schaltkreise möglich.

## 4.2. Spezifische technische Daten

Speicherkapazität 2KByte statischer RAM

(Anordnung von 2x8 Speicherchips)

6K Byte: EPROM

(Anordnung von 6 Speicherchips)

Speicherschaltkreistypen:

Q240

1K x 1 Bit; nMOS

**Q260**

1K x 8 Bit: nMOS

Zugriffszeit: Batriebserten: ≤ 530 ns

Betriebsarten:

Abgeschlossene Zyklen "Lesen" oder "Schreiben" in beliebiger Reihen-folge beim RAM und "Lesen" beim EPROM.

Datenerhalt:

EPROM ist nur extern mit Progremmiergerät möglich).

(Programmieren oder Löschen der

Energieunabhängige Datenspeicherung bei ROM-Speicher.

RAM-Information geht bei Abschaltung der Betriebsspannung verloren. Ein Datenerhalt ist möglich,

wenn im Ruhezustand des Speichers

eine Spannung (Schlafspannung)

von außen über Klemme 5PG zugeführt wird. Die Spannung muß

2 V sein.

Stromversorgung:

5P = 5 V ± 5 %, typ. 0,7 A für ROM-Speicher, Steuerelektronik und Pufferschaltkreise 5PG = 5 V ± 5 %, typ. 0,5 A (bei 2 V Schlafspannung etwa 0,3 A)

für RAM-Speicherschaltkreise

5N = -5 V ± 5 %, typ. 0,2 Å

12P = 12 V ± 5 %, typ. 0,3 Å

Es ist defür zu sorgen, daß die

Spannung 5N nicht später als 10 ms

nach Zuschaltung von 5P bzw. 12P

ihren Kennwert erreicht und höch

stens 10 ms vor Wegfall der 5P

bzw. 12P abschaltet.

4.3.1.

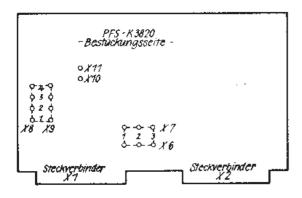

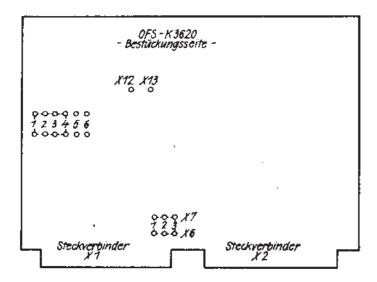

Programmierfelder der Steckeinheit

Abb. IX/6

Die Programmierfelder bestehen aus Wickelstiftpaaren oder Mikroschaltern. Im ersteren Fall erfolgt die Programmierung, indem Wickelstiftpaare nach der Wickeltechnik miteinander verbunden werden.

### 4.3.2.

### Adressenzuordnung

Die 16 Adressignale werden im Speicher wie folgt bewertet:

ABO ... AB9

- interne Chipadressierung

AB12 ... AB15

- Umkodierung in Abhängigkeit von der im Programmierfeld K10:1 ... 4 - Xii:1 ... 4 fixierten Adresse. Die im Speicher wirkseme Adresse AB12K ... AB15K ergibt sich aus der stellenrichtigen Subtraktion der eingegebenen Steckeinheitenadresse von der engelegten Adresse AB12 ... AB15.

AB10, AB11, AB12K - Auswahl einer der 8 1K-Blöcke der STE (Chipauswahl)

AB13K ... AB15K - Auswahl der Steckeinheit, wenn alle 3 Signale Nullpotential besitzen.

Zuordnung des Adresbereichs der Steckeinheit:

Über 4 Wickelbrücken bzw. 4 Schalter X10:1 ... 4, X11:1 ... 4 wird dem Speichermodul ein wählbarer zusammenhängender Adreß-bereich von 8K Adressen zugeordnet.

Des Programmierfeld erhält in binärer Verschlüsselung die Anfangsadresse des gewünschten Adreßbereiches. Diese Adresse ist ein ganzzahliges Vielfaches von 4K.

### Kodetabelle:

| Wickelbrüe | cken |

|------------|------|

|------------|------|

| Adresbereich      | X10:4-X11:4 | X10:3-X11:3 | X10:2-X11:2 | X10:1-X11:1 |

|-------------------|-------------|-------------|-------------|-------------|

| 0000-1 <b>FFF</b> |             | _           |             |             |

| 1000_2FFF         | -           | _           |             | Brücke      |

| 2000-3FFF         | -           | -           | Brücke      | _           |

| 3000-4FFF         | _           |             | Brücke      | Brücke      |

| 4000-5FFF         | -           | Brücke      |             | _           |

| • •               | •           | ·           | <b> .</b>   |             |

| • •               | •           |             | ] <b>.</b>  | •           |

| • •               | •           |             | 1.          | •           |

| ECCO-FFFF         | Brücke      | Brücke      | Brücke      | -           |

Bei Schalterbestückung entspricht "Brücke" dem geschlossenen Schalter.

#### 4.3.3.

#### Vertauschung der RAM/ROM-Bereiche

Um eine gute Flexibilität in der Gestaltung der RAM- und ROM-Bereiche im Gesamtspeicher K 1520 zu gewährleisten, können die RAM/ROM-Bereiche des Speichermoduls adressenmäßig gespiegelt werden. Die Speicherfolge wird mit Kodierbrücke X10:6-X11:6 festgelegt.

X10:6-X11:6

adressenmäßige Speicherfolge

-

2 K RAM, 6K ROM

Brücke

6K ROM, 2K RAM

Bei Schalterbestückung entspricht "Brücke" dem geschlossenen Schalter.

Es ist die unterschiedliche relative Adresse der ROM-Elemente zu beschten.

#### 4.3.4.

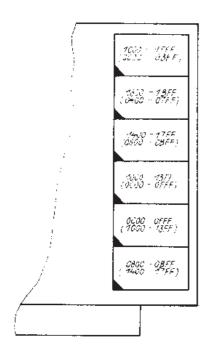

### Plazierung der ROM-Elemente auf der Steckeinheit

Die programmierten ROM-Elemente werden über DIL-Steckfassungen auf der Steckeinheit kontaktiert.

Die einzelnen Steckplätze repräsentieren die im folgenden Schema dargestellten relativen Adreßbereiche der Steckeinheit (bezogen auf die programmierte Steckeinheiten-Anfangsadresse). Die Adreßbereiche unterscheiden sich in Abhängigkeit von der Belegung der Wickelbrücke X10:6-X11:6 (Reihenfolge der RAM/ROM-Speicher).

Die in Klammern dargestellten Adressen gelten für die Speicherfolge 6K ROM, 2K RAM (X10:6-X11:6 gebrückt).

Abb. IX/7

4.3.5.

Auswahl des Speichersperrsignals MEMDI

| Im Speichermodul wirk- | Wickelbrücken |           |           |  |

|------------------------|---------------|-----------|-----------|--|

| same Sperrsignale      | X6:1-X7:1     | X6:2-X7:3 | X6:3-X7:3 |  |

| MEMDI (X1:B09)         | Brücke        | _         |           |  |

| MEMDI1 (X2:A21)        | -             | Brücke    | ***       |  |

| MEMDI2 (X2:B21)        | -             |           | Brücke    |  |

Bei Schalterbestückung entspricht "Brücke" dem geschlossenen. Schalter.

## 4.3.6. "WAIT"-Generierung

Von den dynamischen Daten der aufgerufenen Speicherschaltkreise hängt es ab, ob während des Befehlszyklus im K 1520 eine Zeitverlängerung über "WAIT" vorgenommen werden muß.

Durch die konkrete Bestückung der Steckeinheit ist bereits vorgegeben, wie die Einstellung erfolgen muß.

Für den allgemeinen Anwendungsfall kann die Einstellung wie folgt vorgenommen werden:

Generierung von "WAIT" im M1-Zyklus: Brücke X10:5-X11:5 offen Unterdrücken der "WAIT"-Bildung: Brücke X10:5-X11:5 geschlossen.

## 4.3.7. Betriebsspennungszuführung 5PG

Normalerweise werden die RAM-Speicherbausteine über den Betriebsspannungsanschluß 5PG versorgt. In Sonderfällen, wo die Anschlüsse 5PG auf dem Bus nicht belegt sind, kann 5PG steckeinheitenseitig durch Brückung der Wickelstifts X12-X13 mit 5P verbunden werden.

### 4.4. Funktionsbeschreibung

### 4.4.1. Verwendungszweck

Der OFS K 3620 wird im Mikrorechner K 1520 als kombinierter Operativspeicher (statischer Schreib-Lese-Speicher) und programmierbarer Festwertspeicher (Nur-Lese-Speicher) eingesetzt.

### 4.4.2. Funktion

Die Steckeinheit beinhaltet die Funktionsgruppen Speichermatrix. Ein- und Ausgabepuffer und Auswahl- und Steuerelektronik. Die Wirkungsweise der Schaltung ist im Blockschaltbild Abb. IX/8 dargelegt.

Die Speichermatrix besteht aus 2 Gruppen zu je 8 RAM-Speicherchips Q240 und aus 6 EPROM-Speicherchips Q260. Die ROM-Bausteine sind auswechselbar auf DIL-Steckfassungen gesetzt.

Da der Speichermodul K 3620 eine Kombination der speicherabgerüsteten Moduln K 3520 und K 3820 darstellt, sind auch die Schaltungsdetails praktisch identisch, so daß auf die Beschreibungen der beiden Moduln 2.4.2. und 3.4.2. verwiesen werden kann.

Eine modulspezifische Lösung stellt die Adressenumschlüsselung und die RDY-Bildung der.

Zur Adressenumschlüsselung wird wie beim K 3820 ein Adderbaustein PS83 in dort beschriebener Art und Weise eingesetzt. Entsprechend der vorliegenden Speichergröße werden hier 3 ungeschlüsselte Adreßbits Ab13K ... AB15K zur Blockeinheitenauswahl herangszogen. Um eine wahlweise Adressenspiegelung vornehmen zu können, werden die Adreßbits AB10, AB11 und das umgeschlüsselte Adreßbit AB12K dem 1 aus 8-Dekoder-Baustein SE05 zur Bildung der /CE-Signale über Exklusiv-Oder-Baustufen (PS86) zugeführt. Diese Baustufen negieren die Adreßbits, wenn die Wickelbrücke X10:6-X11:6 geschlossen ist. Diese Negation bewirkt, daß bei aufwärtszählender Adresse die /CE-Signale in abfellender Nummernfolge aktiviert werden. Bei offener Brücke ist diese Nummernfolge steigend.

Diese Schaltungsmaßnahme ergibt eine wahlweise Vertauschberkeit der RAM/ROM-Bereiche des Speichermoduls. Das RDY-Signal wird für die RAM- und ROM-Speicher unterschiedlich gebildet. Beim RAM-Speicher wird das Signal von den /CE-Signalen für die zwei 1K-RAM-Speicherblöcke abgeleitet, während für den ROM-Speicher wie beim K 3820 ein Datenbit des Speicherausgangs ausgewertet wird. Alle Bildungskomponenten des Signals werden disjunktiv zum RDY-Signal verknüpft und auf den Bus gelegt.

Durch die hier gegenüber K 3820 vorgenommene Vertauschung der zwei Eingänge des Komparatorbausteins erreicht man ein negiertes Auswertesignal am Bausteinausgang, so daß die disjunktive Verknüpfung leicht vorgenommen werden kann.